Research Objectives

Three-dimensional (3-D) integration with through-silicon-vias (TSVs) has emerged as an effective approach to overcome the wiring limit beyond the 32 nm technology node for microelectronics. Due to the mismatch of thermal expansion between the via material and Si, thermal stresses ubiquitously exist in the integrated 3-D structures. The thermal stresses can be significant to raise serious reliability issues, such as TSV extrusion and mobility degradation of logic devices. Funded by Semiconductor Research Corporation (SRC), the objectives of this project are: (1) Develop experimental and modeling tools for characterizing the interfacial properties required for reliability and design of 3D integration; (2) Develop a comprehensive methodology to investigate the thermomechanical reliability of TSV structures with the objective to optimize the material and the design of TSV structures for 3D ICs.

Principal Investigators

Paul S. Ho, Kenneth M. Liechti, Rui Huang

Highlights

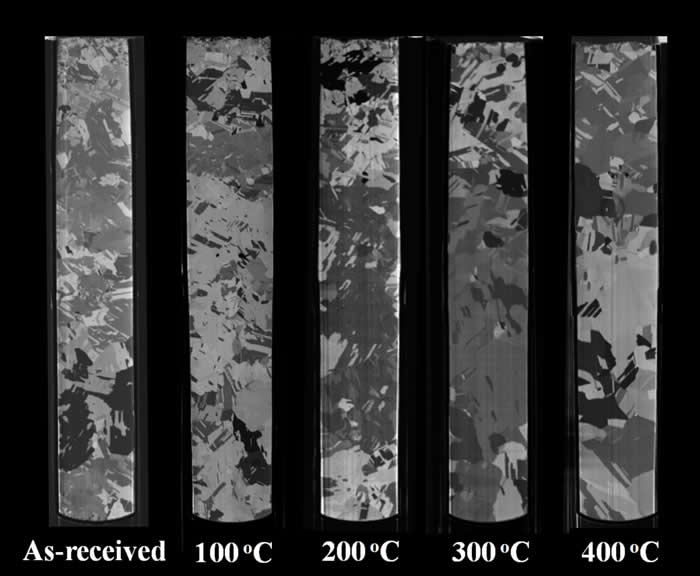

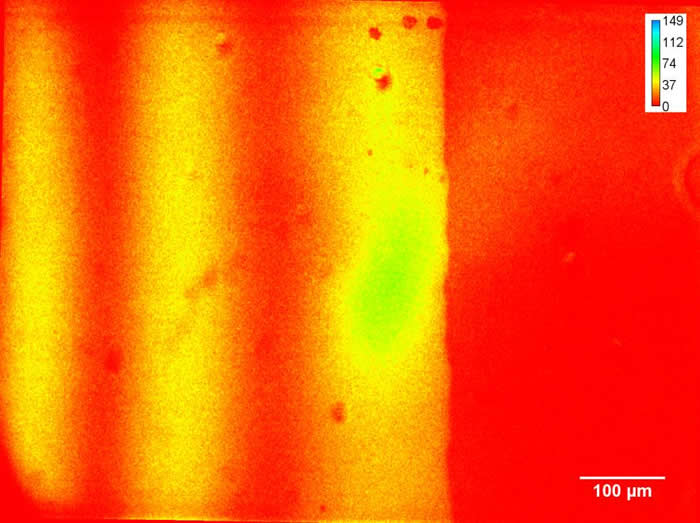

Microtructures and Stress Characterization of Copper TSVs

To understand the characteristics of the thermal stresses in integrated TSV structures, experimental measurements and numerical analysis were performed. A precision wafer curvature technique was used together with micro-Raman spectroscopy to characterize the deformation and stresses in the TSV structures. The microstructures of the Cu vias were analyzed by FIB and EBSD to provide insights to the deformation mechanisms. Guided by the experimental observations, finite element analysis was performed to analyze the thermal stresses taking into account the elastic anisotropy of Si and the plasticity of Cu. It was found that plastic deformation is localized at the top of the Cu vias near the via/Si interface and may play an important role in TSV extrusion. Finally, the effect of thermal stresses on carrier mobility was investigated to evaluate the keep-out zone (KOZ) for logic devices near the TSVs.

Infrared Crack-Opening Interferometry (IR-COI)

Interferometric measurements of the normal crack opening displacements near the crack front in a double-cantilever beam specimen were exploited along with an augmented analytical solution for J-integral to directly extract the traction-separation relations of the interface. Alternatively, as an iterative method, we relied on comparisons of measured crack length and normal crack opening displacements with numerical simulations obtained from two types of candidate traction-separation relations. It was found that the shape of the traction-separation relation, in addition to the interfacial toughness and strength, was needed to bring the numerical solutions into optimal registration with the measurements. On the other hand, the direct method lived up to its name in terms of ease of parameter extraction while providing a reasonable set of parameters.

Selected Publications

- S.-K. Ryu, T. Jiang, J. Im, P.S. Ho, R. Huang, Thermo-mechanical failure analysis of through-silicon via interface using a shear-lag model with cohesive zone. IEEE Trans. on Device and Materials Reliability, accepted (2013). DOI: 10.1109/TDMR.2013.2261300.

- T. Jiang, S.-K. Ryu, Q. Zhao, J. Im, R. Huang and P.S. Ho, Measurement and Analysis of Thermal Stresses in 3D Integrated Structures Containing Through-Silicon Vias. Microelectronics Reliability 53, 53-62 (2013). DOI: 10.1016/j.microrel.2012.05.008.

- S. Gowrishankar, H. Mei, K.M. Liechti and R. Huang, A comparison of direct and iterative methods for determining traction-separation relations. International Journal of Fracture 177, 109-128 (2012). DOI: 10.1007/s10704-012-9758-3.

- S.-K. Ryu, K.-H. Lu, T. Jiang, J. Im, R. Huang, P.S. Ho, Effect of Thermal Stresses on Carrier Mobility and Keep-out Zone around Through-Silicon Vias for 3-D Integration. IEEE Trans. on Device and Materials Reliability 12, 255-262 (2012). DOI: 10.1109/TDMR.2012.2194784. Front cover.

- S.-K. Ryu, Q. Zhao, M. Hecker, H. Y. Son, K. Y. Byun, J. Im, P.S. Ho, and R. Huang, Micro-Raman Spectroscopy and Analysis of Near-Surface Stresses in Silicon around Through-Silicon Vias for Three-Dimensional Interconnects. J. Appl. Phys. 111, 063513 (2012).

- S.-K. Ryu, T. Jiang, K.H. Lu, J. Im, H.-Y. Son, K.-Y. Byun, R. Huang, and P.S. Ho, Characterization of thermal stresses in through-silicon vias for three-dimensional interconnects by bending beam technique. Applied Physics Letters 100, 041901 (2012).

- S.-K. Ryu, K.-H. Lu, X. Zhang, J. Im, P.S. Ho, and R. Huang, Impact of Near-Surface Thermal Stresses on Interfacial Reliability of Through-Silicon-Vias for 3-D Interconnects. IEEE Trans. on Device and Materials Reliability 11, 35-43 (2011). DOI: 10.1109/TDMR.2010.2068572.

- H. Mei, S. Gowrishankar, K. M. Liechti, R. Huang, Initiation and propagation of interfacial delamination in integrated thin-film structures. Proc. 12th IEEE Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems (ITherm), Las Vegas, NV, June 2010. DOI: 10.1109/ITHERM.2010.5501290.