# A silicon-based photocathode for water reduction with an epitaxial $\text{SrTiO}_3$ protection layer and a nanostructured catalyst

Li Ji<sup>1,3,\*</sup>, Martin D. McDaniel<sup>2</sup>, Shijun Wang<sup>3</sup>, Agham B. Posadas<sup>4</sup>, Xiaohan Li<sup>1</sup>, Haiyu Huang<sup>1</sup>, Jack C. Lee<sup>1</sup>, Alexander A. Demkov<sup>4</sup>, Allen J. Bard<sup>3</sup>, John G. Ekerdt<sup>2</sup>, and Edward T. Yu<sup>1</sup>

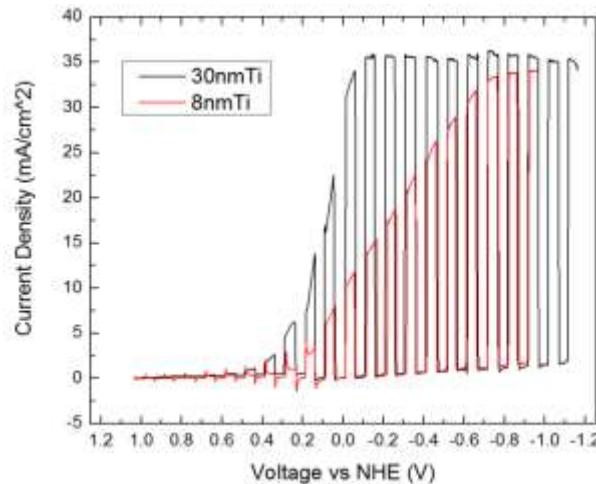

**Supplementary Figure 1 |** Linear sweep voltammetry (LSV) results for 30nm Pt/Ti/4 unit-cell STO/p-Si with 8nm and 30nm Ti. The illumination was chopped during the measurement. 0.5M  $\text{H}_2\text{SO}_4$  was used as electrolyte.

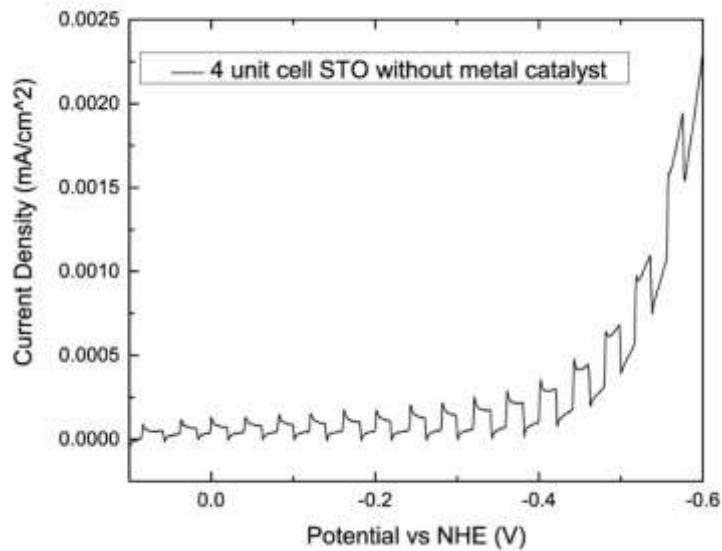

**Supplementary Figure 2 |** LSV results for 4 u.c. STO/pSi without any metal catalyst. The illumination was chopped during the measurement. 0.5M H<sub>2</sub>SO<sub>4</sub> was used as electrolyte.

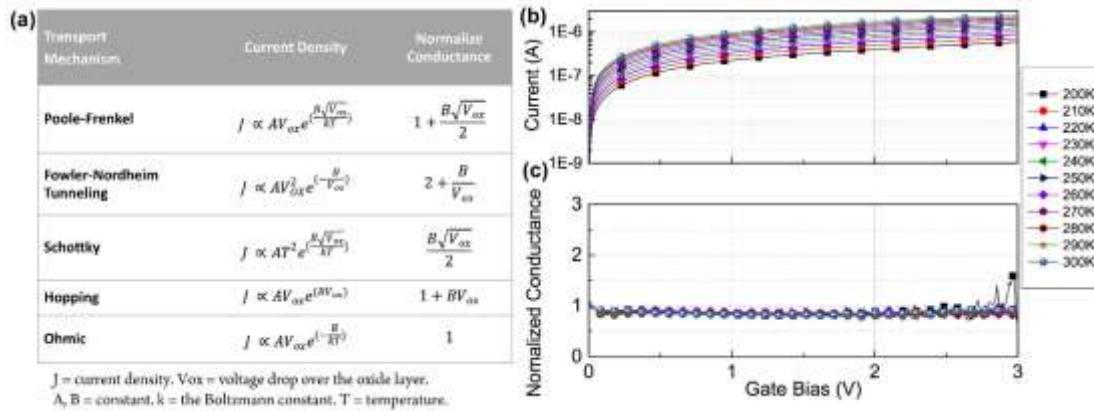

**Supplementary Figure 3 |** (a) Figure S3 (new). (a) Table of transport mechanisms (b) I-V measurements and (b) normalized conductance  $G_n = (dI/dV)/(I/V)$  in rough vaccum under various temperatures. The voltage is applied to the top metal contact. The electrical measurements is conducted by Agilent B1500A Semiconductor Device Analyzer.

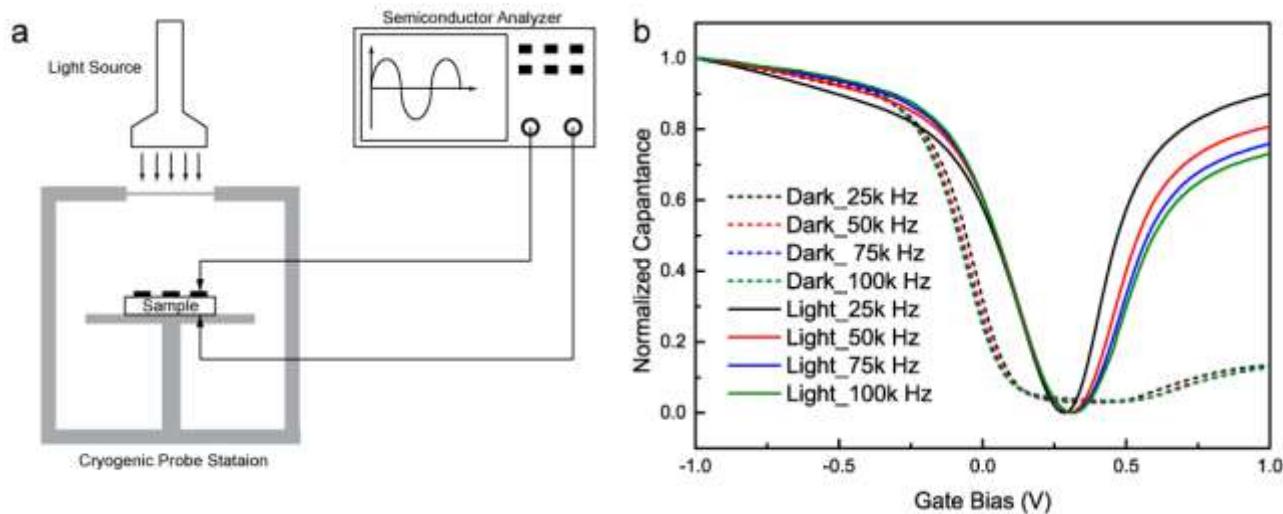

**Supplementary Figure 4 | (a)** Schematic of the measurement apparatus and configuration. **(b)** Normalized capacitance for 4 unit-cell STO sample with 400  $\mu\text{m}$  diameter metal dots as the top contact under dark and light conditions. The voltage is applied to the gate (top contact). In dark, it is normal high-frequency response for MOS capacitor. At room temperature, the minority carrier response is much slower and not instantaneous over the frequency range from 25k  $\sim$  100k Hz. So at positive bias, the capacitance is low. However, when illuminated, the capacitance increased rapidly to a value greater than the thermal equilibrium value in the dark by increasing steady-state carrier concentration generated by the light. The gate electrode is sufficiently thick and opaque and has no scratches or pinholes. The minority carriers generated within a diffusion length of the gate will form an inversion layer under the gate.

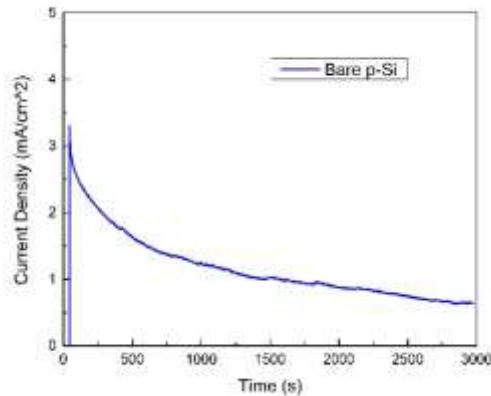

**Supplementary Figure 5 |** Stability test for bare p-Si wafer in 0.5M H<sub>2</sub>SO<sub>4</sub> under -0.2V bias vs NHE. These results agree well with previous work<sup>1</sup>.

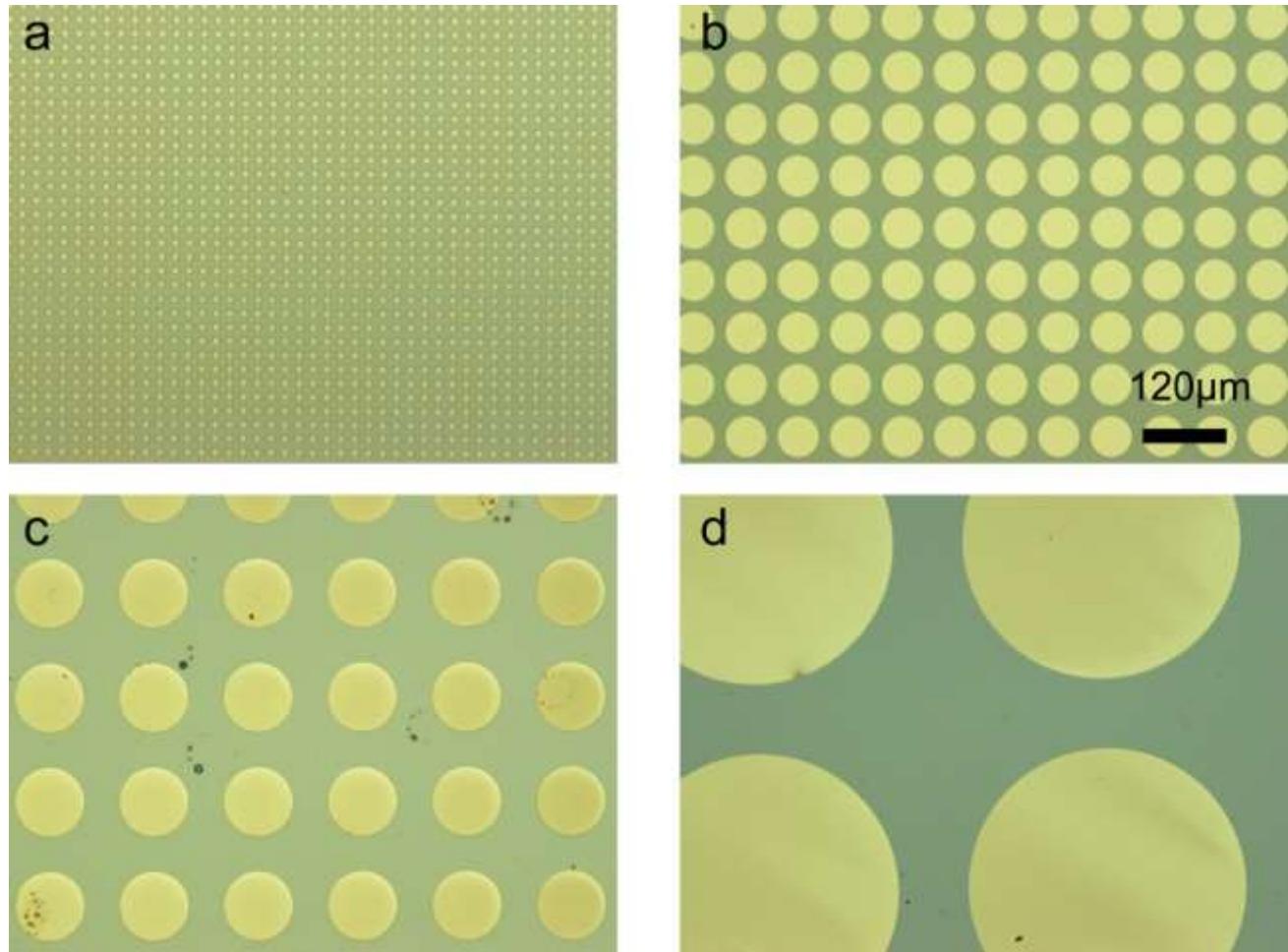

**Supplementary Figure 6** | Optical Microscopy image of Ti/Pt bilayer metal catalyst with various diameter/spacing fabricated by photolithography. (a) 1 μm/2 μm. (b) 60 μm/75 μm. (c) 100 μm/125 μm. (d) 400 μm/500 μm.

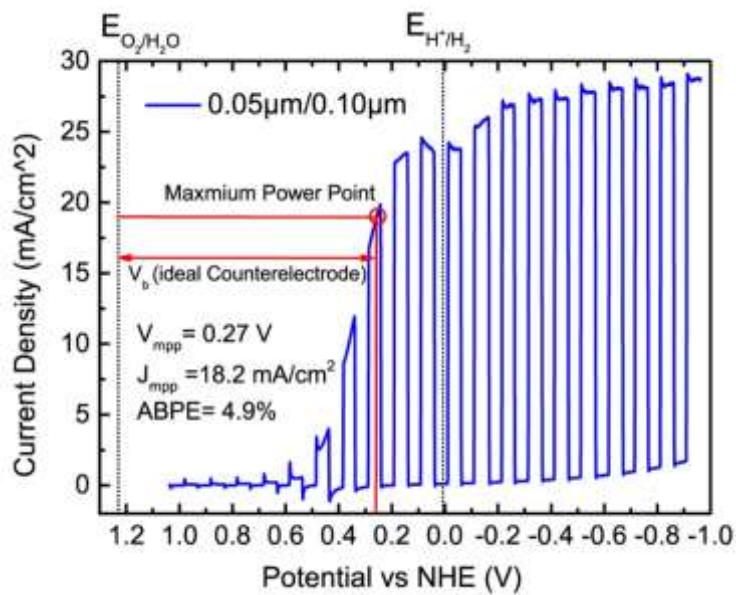

**Supplementary Figure 7** | LSV results of 20nmPt/30nmTi/4 u.c. STO/pSi sample with 0.05μm/0.1μm via nanosphere lithography and corresponding ABPE calculation. The illumination was chopped during the measurement. 0.5M H<sub>2</sub>SO<sub>4</sub> was used as the electrolyte.

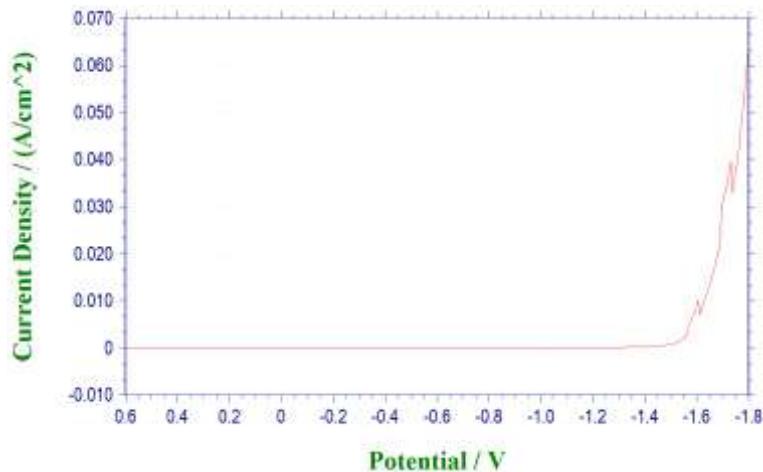

**Supplementary Figure 8** | LSV results for p-Si wafer we used as substrate in this work. No HF treatment was applied. The illumination was chopped during the measurement. 0.5M H<sub>2</sub>SO<sub>4</sub> was used as the electrolyte.

## References

1. Sim U, *et al.* N-doped monolayer graphene catalyst on silicon photocathode for hydrogen production. *Energ Environ Sci* **6**, 3658-3664 (2013).