# Graphene and two-dimensional materials for silicon technology

Deji Akinwande<sup>1</sup>\*, Cedric Huyghebaert<sup>2</sup>, Ching-Hua Wang<sup>3</sup>, Martha I. Serna<sup>1</sup>, Stijn Goossens<sup>4</sup>, Lain-Jong Li<sup>5</sup>, H.-S. Philip Wong<sup>3,5</sup> & Frank H. L. Koppens<sup>4,6</sup>

The development of silicon semiconductor technology has produced breakthroughs in electronics—from the microprocessor in the late 1960s to early 1970s, to automation, computers and smartphones—by downscaling the physical size of devices and wires to the nanometre regime. Now, graphene and related two-dimensional (2D) materials offer prospects of unprecedented advances in device performance at the atomic limit, and a synergistic combination of 2D materials with silicon chips promises a heterogeneous platform to deliver massively enhanced potential based on silicon technology. Integration is achieved via three-dimensional monolithic construction of multifunctional high-rise 2D silicon chips, enabling enhanced performance by exploiting the vertical direction and the functional diversification of the silicon platform for applications in opto-electronics and sensing. Here we review the opportunities, progress and challenges of integrating atomically thin materials with silicon-based nanosystems, and also consider the prospects for computational and non-computational applications.

dvances in semiconductor technology have manifested in the doubling of the number of components (for example, transistors) per die at a regular interval (for example, every two years), which is loosely called Moore's law. In 2018, the semiconductor industry crossed the 10-nm threshold to offer silicon logic technologies at the 7-nm technology node, with the 5-nm and 3-nm nodes expected in the foreseeable future. (A technology node is a generation of semiconductor manufacturing processes associated with a particular size.) Meanwhile, memory technologies have already changed course and departed from the traditional scaling of geometry. Dynamic random access memory (DRAM) has virtually stopped dimensional downscaling, and has transitioned into the stacking of DRAM chips with logic chips to provide the memory capacity, reduced latency and increased bandwidth required of today's computing systems. Flash memory (in particular, NAND flash), which has become the dominant non-volatile data storage device, has also stopped dimensional downscaling in the 2D plane of the chip. Current and future generations of flash memory are providing increasingly larger storage capacity by building up multiple layers of memory cells in the third dimension, in a way akin to a high-rise building. Flash memories with 64 layers were already in production in 2018, with further opportunities for taller, high-rise memory chips.

#### Silicon wonderland

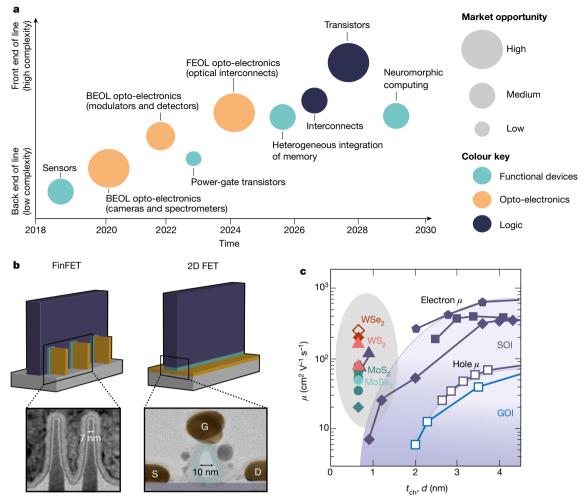

Will future logic technologies continue to provide the energy efficiency required of computing systems? Will emerging applications (for example, in optoelectronics and sensors) and future computation workloads (such as neuromorphic and quantum computing) demand new materials and device concepts compatible with Si CMOS integration? How will technology progression be assessed now that the linear dimensions of devices have ceased to serve as a meaningful metric? In the same sense, how will the added value of integrating 2D materials (2DMs) and new materials be evaluated? These are some of the most pressing questions facing the semiconductor industry today. They are in particular put in a special context by considering the many advantages

and diverse functions that are afforded by 2DMs, which can have a massive economic impact in leveraging ubiquitous Si technology (see Fig. 1a).

#### Smaller is better

The advances of key metrics such as power–performance–area (and cost reduction) of semiconductor technology in the past five decades have mostly been achieved through dimensional scaling<sup>1</sup>. The principle of device scaling introduced by Dennard provides a guideline to scale down a field-effect transistor (FET) to a small size by proportionally scaling down all physical dimensions simultaneously while scaling up the doping concentration of the transistor channel<sup>2</sup>. By the late 1990s, it was becoming increasingly clear that this constant-field scaling had reached its limits owing to the increasing difficulty in achieving complex doping profiles and the excessive leakage current through the thin silicon dioxide gate insulator<sup>3</sup>. Thus began the 'equivalent scaling' era of the past two decades, which saw the introduction of strained silicon to enhance current drive<sup>4</sup>, and high dielectric constant (high-*k*) gate dielectrics and metal gate electrodes<sup>5</sup> as a way to continue the performance and cost benefits expected of Moore's law.

Nevertheless, controlling short-channel effects for sustained dimensional scaling remains a critical challenge. Towards the end of the last millennium, emerging research began to explore a new concept, named the Scale Length Theory  $^{6-8}$ , which relates the transistor's electrostatic integrity to a natural scale length ( $\lambda$ ) that is a function of the gate/channel geometry, thicknesses and dielectric constants. A FET would not suffer from short-channel effects if the gate length maintained a certain aspect ratio to the scale length, even for a channel without doping. The state-of-the-art FinFET transistors (Fig. 1b) guided by this theory have been in volume production since the 22-nm node (about 2012)  $^9$ . For the 10- and 7-nm technology nodes, the gate lengths of FinFETs are about 20 nm, and the fin thickness is about 7–8 nm. Multiple-stacked nanowires and nanosheets with wrap-around gates are being developed to provide even better electrostatic control. As transistor width

<sup>1</sup>Microelectronics Research Center, Department of Electrical and Computer Engineering, The University of Texas at Austin, Austin, TX, USA. <sup>2</sup>IMEC, Leuven, Belgium. <sup>3</sup>Department of Electrical Engineering, Stanford University, Stanford, CA, USA. <sup>4</sup>ICFO–Institut de Ciencies Fotoniques, The Barcelona Institute of Science and Technology, Castelldefels (Barcelona), Barcelona, Spain. <sup>5</sup>Corporate Research, Taiwan Semiconductor Manufacturing Company (TSMC), Hsinchu, Taiwan. <sup>6</sup>ICREA–Institució Catalana de Recerça i Estudis Avancats, Barcelona, Spain. \*e-mail: deji@ece.utexas.edu

**Fig. 1** | **Potential applications of 2DMs and modern transistor devices. a**, Applications of 2DM–Si technology mapped in time and integration complexity. The area of the circles is a rough qualitative estimate of addressable market opportunity (from refs <sup>34,117</sup>). The position of a circle indicates the time when the first products with the 2DM-based technology could potentially be introduced. Complexity increases when moving from back end of line (BEOL) to front end of line (FEOL) integration. **b**, Left, state-of-the-art FinFET transistor in production (adapted with permission from ref. <sup>118</sup>, IEEE). Right, an example of a planar 2D FET being

can only increase by adding a discrete number of fins or nanowires, multiple-stacked nanosheet FETs offer the additional benefit of continuous transistor widths 10. To provide for higher device density and the associated cost reduction, one must continue to shrink the gate length and thus a thinner channel is required. Because the carrier mobility and transport along the thin-body channel of three-dimensional (3D) bulk semiconductors degrades substantially for thicknesses below 3 nm (Fig. 1c) 11, a new channel material that is thin and yet maintains good carrier transport is required.

#### The rise of 2DMs

2D layered semiconductors have emerged as plausible candidates for FETs that require extremely thin channels because many 2DMs maintain good carrier transport even for atomically thin layers below 1 nm. For instance, the scale length for planar 2D FETs is approximately<sup>6</sup>:

$$\lambda \approx t_{\rm ch} + \frac{\varepsilon_{\rm ch}}{\varepsilon_{\rm ox}} t_{\rm ox}$$

where  $t_{\rm ch}$  and  $\varepsilon_{\rm ch}$  are the channel thickness and channel k, respectively, and  $t_{\rm ox}$  and  $\varepsilon_{\rm ox}$  are, respectively, the thickness and k of the gate oxide. Notably,  $\lambda$  approaches 1 nm for monolayer transition-metal

considered for future technology generation (adapted with permission from ref.  $^{12}$ , IEEE). The upper panels show structural diagrams (dark blue, gate; brown, channel; light blue, gate dielectric; grey, substrate) and the lower panels show images of parts of an actual device, originating from the positions shown boxed above.  $\mathbf{c}$ , Mobility ( $\mu$ ) versus channel thickness ( $t_{\rm ch}$ ) for semiconducting channels of TMDs $^{12}$  (within the ellipse) and for ultrathin silicon-on-insulator (SOI) and germanium-on-insulator (GOI) devices $^{110}$  (blue shaded areas). Filled (open) symbols represent electron (hole) mobilities. Adapted from ref.  $^{11}$ , American Chemical Society.

dichalcogenides (TMDs) using high-k dielectrics (k > 10) with thickness below 2 nm, revealing the promising scalability of 2D FETs. Indeed, high-bandgap MoS<sub>2</sub> FETs with 10-nm gate length have been successfully demonstrated (Fig. 1b) with good subthreshold slope (80 mV per decade) and high 'on' currents  $(>400 \,\mu\text{A}\,\mu\text{m}^{-1})^{12}$ . Moreover, using a nanotube as the gate electrode, a  $MoS_2$  FET with 1-nm gate length has been reported<sup>13</sup>. With lower-bandgap, higher-mobility materials such as black phosphorus, larger 'on' current (of about 1 mA μm<sup>-1</sup>) is achievable<sup>14</sup>. It is also important to recognize that the use of 2D channel materials is compatible with other performance-enhancing technologies, such as (but not limited to) the use of negative capacitance to boost gate-to-channel coupling 15,16 and the use of stacked layers of channel materials to boost current drive per area. In addition, 2D FETs can be fabricated at low temperatures, a key requirement for attaining the next level of computing performance and energy efficiency using monolithic 3D integration of logic and memory<sup>17</sup>.

#### Non-computational systems

Beyond the endless interest in advancing modern Si electronics by exploiting the intrinsic scalability and low-power benefits of 2DMs for computational systems as mentioned above, there exists also an ever-widening opportunity to employ these atomic materials for

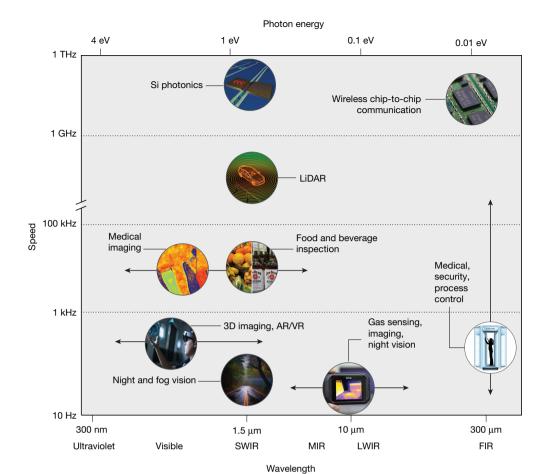

**Fig. 2** | **Optoelectronic applications.** Technology areas of 2DM-based integrated opto-electronics, mapped in terms of required speed and operational wavelength range (lower *x* axis; the upper *x* axis gives the corresponding photon energy). AR, augmented reality; VR, virtual reality; SWIR, short-wave infrared; MIR, mid-infrared; LWIR, long-wave infrared;

FIR, far infrared. Image credits: top row, left, adapted with permission from ref. <sup>119</sup>; second row, Shutterstock (https://www.shutterstock.com); third row, left, adapted with permission from ref. <sup>120</sup>; bottom row, leftmost and rightmost, Shutterstock.

non-computational systems 18-26, such as photodetectors and modulators for image sensors, light detection and ranging (LiDAR) and data communications (Fig. 2), as well as lasers, piezoelectrics, nano-electromechanical systems (NEMS), radio-frequency devices, magnetic devices, Hall sensors, and all sorts of gas, chemical and biological sensors. These diverse applications can be categorized as noncomputational systems (colloquially termed 'more than Moore') and ideally realized on an integrated CMOS chip where Si devices provide the driver, read-out and peripheral circuitry necessary to form a complete system. Towards this goal, fully integrated prototype graphene-Si chips have been recently demonstrated, including graphene gas sensors<sup>20</sup>, optical receivers<sup>27</sup> and image sensor arrays<sup>19</sup> on top of foundry or commercial chips with Si read-out electronics. (Here a foundry is a semiconductor business that manufactures the designs of other companies.) Furthermore, biomedical sensors featuring graphene transistors on Si substrates have been substantially advanced and are now available as a commercial product<sup>28</sup>. Progress towards TMD integration with Si chips is ongoing and will very much benefit from the back-end-of-line (BEOL) process techniques developed for graphene integration.

#### Image sensors and spectrometers

Digital camera technologies have experienced a revolution in the past 20 years, thanks to the progress of CMOS-based image sensors, in terms of low-cost manufacturing, high resolution, high performance and compact footprint. The image sensor market was valued at \$15 billion in  $2017^{29}$ , and is predicted to grow, in part driven by the automotive, mobile and medical markets. Current low-cost and high-performance image sensors are based on silicon detectors integrated with a CMOS

read-out integrated circuit, and in general they are sensitive only to the visible and near-infrared range (300–900 nm wavelength).

Considering the full infrared range of the spectrum, a much wider range of applications (such as night and fog vision, biomedical imaging, food inspection, gas detection and security) can be addressed; see Fig. 2. Even at longer wavelengths, terahertz rays can penetrate commonly used dielectric materials and allow detection of substancespecific spectroscopic features. The cost of image sensors for the infrared and terahertz range is much higher, because integration with Si CMOS is not monolithic and therefore more challenging. For example, image sensors based on III-V materials are bonded to CMOS read-out integrated circuits die by die, in contrast to Si CMOS image sensors. This limits the pixel pitch (typically  $>12 \mu m$  for commercial technology) and increases the cost (>\$10,000 for a one-megapixel InGaAs camera). For room-temperature imaging of mid-infrared (thermal) radiation, silicon bolometers integrated with CMOS electronics are the leading technology. The speed (typically <50 frames per second), sensitivity and resolution are limited ( $<10^5$  pixels).

In addition, many spectroscopic applications need access to the visible and infrared range at the same time. Another emerging imaging technology is 3D imaging for autonomous vehicles and augmented/virtual reality markets. Extension of 3D imaging into the infrared range gives less interference of ambient background light, and enables lower power consumption of active sources.

As the applications mentioned above require at the same time sensitivity to a broad wavelength band, low power, and low-cost production and integration, it is clear there is a strong need for a suitable (3D) imaging and photosensing platform that is monolithically integrable

## RESEARCH REVIEW

with Si CMOS. 2DM-based photodetectors meet this need, and afford a fast broadband solution across the full spectral range from terahertz to ultraviolet<sup>30</sup>, and can be integrated monolithically with Si CMOS readout integrated circuits in a BEOL process<sup>19</sup>.

#### Integrated photonics

Future data communication technologies, notably 5G, will require several orders of magnitude more bandwidth, attributable to the growth of the internet of things, autonomous vehicles, machine communication, and so on<sup>31</sup>. It is expected that silicon photonics will become the key enabler for high-density optical communications with low power consumption<sup>32,33</sup>, and is likely to be used more and more in data and regional and long-haul communications, as well as in access networks. Integrated photonic devices operate as the optical link, where data from the electrical domain are transferred to the optical domain (via modulators), then transported with very low power loss and subsequently converted back to the electrical domain (via photodetectors). The requirements for integrated photonics are very stringent: high speed, small footprint, low energy consumption and low-cost manufacturing. Current Si photonics technology is based on Si modulators and Ge photodetectors integrated on Si waveguides, with continuing efforts exploring other III-V technologies. 2DMs have emerged as the active detector and modulator components with the potential to overcome the integration, cost and power consumption challenges<sup>34</sup>.

#### **Integrated 2DMs on silicon**

#### **Transistors**

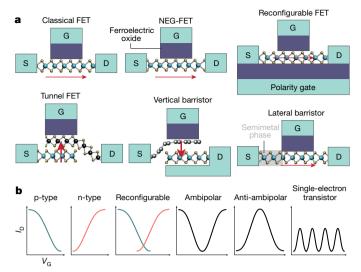

In modern technology, FETs have been the most important electronic devices, with silicon by far the most dominant semiconductor. For this reason, augmenting, rather than replacing, Si CMOS technology with 2D transistors is of central interest from the industrial perspective. At the outset, extensive studies were focused on graphene transistors with much of the resulting innovation and development subsequently applied to TMD FETs, particularly with respect to common issues such as material quality, contacts, dielectrics, doping and substrates<sup>35–37</sup>. The widespread research on 2D transistors has been very fruitful, resulting in an assortment of classical and unique ultrathin-body device structures with diverse electrical characteristics (Fig. 3). A major feature of most of the device structures is the inherent planar profile on account of the atomic sheet, which, combined with a low-temperature integration scheme, makes it straightforward to realize on virtually any level of a standard Si CMOS process flow.

For instance, the classical 2D FET (Fig. 3a) can produce n-type, p-type and ambipolar characteristics depending on the semiconductor, contact and doping. MoS<sub>2</sub> and MoSe<sub>2</sub> are typically n-type devices, while black phosphorus and intrinsic TMDs offer ambipolar characteristics that can be selectively engineered for p- or n-type transport. For more energy-efficient transistors based on improved gate coupling, the ordinary gate dielectric can be replaced by a ferroelectric insulator <sup>16</sup> such as  $HfO_x$ . Still steeper-slope turn-off characteristics can be achieved with a semiconductor-semiconductor atomically thin heterostructure that facilitates quantum mechanical tunnelling, commonly referred to as a tunnel FET (Fig. 3)<sup>38,39</sup>. Similarly, non-tunnelling vertical transport can be realized in other combinations of stacked heterostructures where the channel length can be as short as the thickness of two monolayers<sup>39</sup>, about 1 nm or 1.5 nm for graphene-TMD or TMD-TMD heterostructures, respectively. Another emerging implementation is the so-called barristor, consisting of a semimetal-semiconductor Schottky-barrier junction. It is worth noting that both the tunnel FET and the barristor can also be realized with planar heterojunctions (Fig. 3a). In addition, unconventional device concepts such as the reconfigurable FET and the single-electron transistor (Fig. 3b) have been adapted to 2DMs with enhanced performance<sup>40,41</sup>.

Invariably, these various 2D transistor characteristics present an opportunity for an expanded design space for 3D electronics founded on robust Si VLSI technology. However, there are several challenges in terms of optimizing the material integration and device structure for

Fig. 3 | Examples of 2D transistor devices and transport characteristics. a, Illustration of various 2D planar device structures that can be readily integrated on virtually any level of a high-rise 3D silicon chip (S, source; G, gate; D, drain; NEG-FET, negative-capacitance FET). The tunnel FET is a semiconductor-semiconductor heterojunction and the barristor (vertical or lateral) comprises a semimetal-semiconductor junction. The reconfigurable FET has an additional gate, known as the polarity gate, which regulates the Schottky barrier at the metal-(ambipolar) semiconductor contact, thereby selecting on-demand either electron flow (n-type) or hole flow (p-type). These are simplified illustrations. Advanced device structures can utilize self-aligned gates or doping to minimize contact resistance, dual gates for better electrical control, and patterned polarity gates to reduce capacitance. Arrows represent the primary direction of carrier flow. b, The diverse electrical characteristics (drain current,  $I_D$ , versus gate voltage,  $V_G$ ) afforded by 2D FETs are based on material choice and engineering of the device structure, contacts and doping. The single-electron transistor can be operated at low temperatures with constrictions or opaque contacts. This diversity opens up the design space for advanced 3D electronics.

maximum performance. Here, we highlight three device issues common to all the aforementioned transistor structures, namely contact resistance ( $R_{\rm c}$ ), doping and dielectrics/encapsulation. High contact resistance undoubtedly limits the maximum drive current in most 2D FETs. Nonetheless, in-depth research has demonstrated that relatively low  $R_{\rm c}$  (less than about 200  $\Omega$   $\mu$ m) is achievable with good contacts  $^{36,42}$ . In the ideal limit, even lower  $R_{\rm c}$  can be achieved at metal–TMD contacts according to the inverse relation  $^{42}$   $R_{\rm c} \propto n_q^{-x}$ , where  $n_q$  is the charge doping density and x is between approximately 1 and 1.2. A value of  $n_q > 10^{13}$  cm $^{-2}$  can produce  $R_{\rm c} < 100~\Omega$   $\mu$ m, which satisfies the requirement of the 2015 edition of the international technology roadmap for semiconductors (ITRS) for scaled devices  $^{39}$ .

Contact doping is also beneficial for selecting the polarity of charge flow in ambipolar 2D semiconductors. However, conventional doping by ion implantation is not suitable for atomic materials due to physical damage, hence several alternative methods have been explored, with mixed results <sup>36,43</sup>. For practical adoption, process-friendly air-stable methods are most desirable and in this regard charge transfer from solid dopants using non-stoichiometric high-*k* dielectrics via industry-friendly atomic layer deposition appears promising <sup>44</sup>.

Another principal issue is dielectrics. 2D electron devices experience a performance boost when encapsulated with hexagonal boron nitride (hBN), a 2D dielectric, which offers a clean and smooth interface<sup>35,36,43,45</sup>. Despite the consensus on the benefits of hBN, progress towards wafer-scale uniform growth with quality comparable to exfoliated crystals has been rather limited. Therefore, alternative dielectrics are needed, at least in the near term. In this regard, we argue that some of the main attributes of hBN, such as the clean and smooth surface, can be accessed to some degree in conventional ALD (atomic layer

Fig. 4 | Examples of the use of 2DMs in emerging memory types. a, Monolayer graphene serves as an in-plane electrode in a 3D vertical RRAM to minimize the vertical thickness of the 3D stack  $^{50}$ . BE, bottom electrode; TE, top electrode. b, Graphene is inserted between the  $Ge_2Sb_2Te_5$  (GST) phase-change material and the bottom electrode in a PCM, and acts as a heat concentrator to reduce programming current  $^{52}$ . c, Multi-layer graphene (MLG) is used to suppress capacitive coupling between memory cells, replacing the thick metal/nitride floating gate in

conventional flash memory cells<sup>53</sup>. **d**, 2DMs in a vertical metalisulator–metal (MIM) structure show a non-volatile memory effect down to a monolayer of hBN or TMDs<sup>55–58</sup>. **e**, Non-volatile switching behaviour is observed in the in-plane direction in gate-controlled MoS<sub>2</sub> lateral devices based on grain boundaries instead of filaments<sup>59</sup>. **f**, A 2DM channel is integrated with a ferroelectric memory layer to avoid diffusion of atoms from the ferroelectric material into the semiconductor transistor channel<sup>54</sup>. See main text for details of these memories.

deposition) dielectrics that can be engineered with a fine surface using precision nanofabrication processes. Moreover, ALD dielectrics like BeO that can also afford high thermal conductivity and optical phonon energies<sup>46,47</sup> may further deliver hBN-like benefits for 2D FETs.

#### Memory

Solid-state memories and data storage devices have fundamentally changed the way we store and manipulate data. Consumer products such as smartphones are made possible by flash memory. Invariably, there is insatiable demand for higher-density, higher-capacity, lower-power, solid-state data storage devices. Today's computation work-load requires access to massive amounts of data, resulting in substantial latency and energy consumption in moving data between off-chip memory (typically DRAM) and on-chip computation, a key bottleneck known as the memory wall<sup>48</sup>. To solve this problem, innovations that will provide large-capacity memory on the same chip as the computation units is called for.

Fortunately, over the past two decades, there have been plenty of innovations in memory and data storage devices. This includes non-volatile-memories, such as RRAM (resistive random-access memory), PCM (phase-change memory) and FeRAM (ferroelectric random-access memory)<sup>49</sup>. 2DMs have a wide range of physical characteristics that can potentially improve these emerging memories to a point where they become useful, as illustrated in Fig. 4. For instance, Sohn et al.<sup>50</sup> used graphene as the plane electrode of a 3D vertical RRAM. Graphene minimizes the vertical layer thickness and thereby allows more than 200 layers of vertical RRAM for high density and low cost. Similar to RRAM, PCM is a resistance-based memory but exhibits better endurance, with a lifetime<sup>51</sup> of more than 10<sup>9</sup> cycles. However, the switching physics involve Joule heating of the PCM. To reduce PCM power consumption, Ahn et al.<sup>52</sup> used graphene as a thermal barrier between phase-change material, Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub>, and the bottom electrode (Fig. 4b), concluding that the small out-of-plane thermal conductivity of graphene confined the generated heat, resulting in about 40% less reset current. 2DMs have also shown promise for flash memory. For example, replacing the thick metal/nitride floating gate with one made from thinner multi-layer graphene (Fig. 4c) can suppress capacitive coupling between memory cells $^{53}$ . In ferroelectric memory, the direction of spontaneous electric polarization is used to store binary states. Much research effort has been devoted to integrating graphene, TMDs and black phosphorus<sup>54</sup> to FeFETs, as 2DMs naturally prevent diffusion of atoms from the ferroelectric material that cause interface instability (Fig. 4f).

In addition to integration with the conventional memory, novel switching mechanisms are also observed in 2DMs in a metal–insulator–metal (MIM) structure, as illustrated in Fig. 4d. Lanza and co-workers reported multilayer hBN RRAM attributed to filamentary migration of metallic ions along hBN grain boundaries or defects, a phenomenon also reported in monolayer hBN $^{56}$ . Ge et al.  $^{57}$  reported non-volatile switching in monolayer MoS $_2$ , MoSe $_2$ , WS $_2$  and WSe $_2$ , alluding to a universal effect in TMD atomic sheets. Their area-dependent studies of MoS $_2$  memory is consistent with the theory of localized filaments. Non-volatile switching based on phase transition is also proposed in some 2DMs close to a phase boundary, such as  $^{58}$  Mo $_{1-x}W_x$ Te $_2$ . A memory effect is also observed in planar MoS $_2$  configured in a transistor-like device structure (Fig. 4e), where the mechanism is based on grain boundaries  $^{59}$ .

Beyond memory elements, 2D transistor selectors can be useful for avoiding sneak currents (unwanted leakage currents) in memory arrays. Current 2D FET selectors employ MoS<sub>2</sub> as it is the most common 2D semiconductor, demonstrating  $^{60}$  'off' currents below 2 fA  $\mu m^{-1}$ . In the same spirit, integrating MoS<sub>2</sub> with a capacitor in a one transistor, one capacitor (1T1C) DRAM cell can increase the retention time  $^{60}$ . These effects—reduction in 'off' current and improvement in retention time—are due to the large bandgap of MoS<sub>2</sub>.

#### Interconnects

Over the last few technology generations, circuit delay due to wires has required more frequent insertion of buffers, which results in larger chip area and additional power consumption, diminishing the performance gains made by transistor scaling. Since the 130-nm technology node, copper has become the dominant interconnect material owing to its superior properties compared to aluminium. However, at smaller wire pitches, the resistance of Cu interconnects rises rapidly due to surface and grain-boundary scattering<sup>61</sup>, and also to increased self-heating. Industrial practice is to use metals that have a better trade-off between reliability and wire resistance (for example, cobalt).

When Cu interconnects are used, diffusion barriers such as TaN prevent Cu from diffusing into the dielectric between two interconnects, causing short circuits. Although the barrier material is relatively thin (about 3 nm), it is still too thick because the total wire width is less than 20 nm and the barrier material is less conductive, resulting in a higher effective resistivity of the wire. Moreover, conventional barrier materials lose their ability to block Cu diffusion at thicknesses below a few nanometres. Present industry considerations include the use of ultrathin alternative Cu barrier materials, or switching to metals that

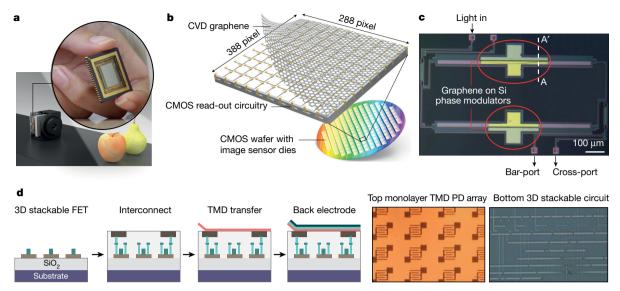

**Fig. 5** | **Integrated graphene and 2D photodevices. a**, Artist's impression of a broadband camera setup based on CMOS-integrated graphene—quantum dot photodetectors. Inset, a photograph of the packaged monolithically integrated graphene-based image sensor. Image adapted from ref. <sup>19</sup>, Springer Nature. **b**, Schematic representation of the integration process. Graphene was transferred on a read-out-integrated circuit die and processed into photodetectors by contacting, patterning and sensitization with colloidal quantum dots. Image adapted from ref. <sup>19</sup>, Springer Nature.

do not require a barrier layer. Single-layer graphene is an effective Cu diffusion barrier despite its atomic thinness  $^{62}$ , with analysis predicting an 8% boost in processor speed mainly due to reduced effective resistivity  $^{63}$ . Besides graphene,  $MoS_2$  and hBN are also capable of suppressing Cu diffusion into surrounding dielectrics  $^{64}$ . It is also important that a CMOS compatible process is available for integrating these new materials into the nanoelectronic fabrication process. Li et al.  $^{65}$  reported graphene growth directly on a Cu wire at a temperature below  $400\,^{\circ}\text{C}$ .

In short, 2DMs would be beneficial for lower-level, tight-pitched metal wires. In this regard, engineered 2D wires—such as FeCl<sub>3</sub>-doped multilayer graphene ribbons—have higher current-carrying capability and improved resistivity (compared to Cu wires scaled below 30 nm); such wires are therefore potential candidates to augment Cu interconnects for future technology nodes that require smaller wires<sup>66</sup>.

#### Graphene-integrated photonics

Graphene detectors, modulators and switches have a wide range of advantages, as they offer high speed, wide spectral bandwidth, low power consumption and monolithic integration with Si CMOS electronic drivers<sup>30,34</sup>. In addition, the production process is very versatile: very similar fabrication processes can be used to make ultrafast photodetectors, modulators and switches. One graphene layer can be used to gate another graphene layer, and so there is no need for chemical doping. Devices based on such double-layer designs can be used for both detector and modulator<sup>67,68</sup>. Owing to its broadband character, graphene has been integrated with several types of optical circuitry based on Si (using wavelengths around 1,500 nm) or SiN (wavelengths around 800 nm)<sup>34</sup>. Moreover, graphene-based modulators can operate<sup>68</sup> with a drive voltage below 2 V, and thus can be driven by conventional CMOS circuitry. Both phase and absorption modulators have been integrated with silicon photonics, and high-rate (10 Gbit s<sup>-1</sup>) binary transmission of a non-return-to-zero data stream over 50 km of single-mode fibre was recently demonstrated<sup>69</sup> (Fig. 5c). A comparison of the relevant figures of merit using commercial and competing technologies is provided in the tables of ref. <sup>34</sup>.

In addition, photodetectors with an operation speed above 180 Gbit s<sup>-1</sup> have been realized<sup>70,71</sup> by exploiting the ultrafast dynamics of photothermoelectric effects. Using gate-defined junctions<sup>72</sup>,

c, Graphene-silicon phase modulators with gigahertz bandwidth. The bar port and cross port are the Mach–Zehnder interferometer optical outputs. Image adapted from ref. <sup>69</sup>, Springer Nature. d, A monolithic 3D image sensor with an integrated phototransistor array fabricated by using a large-area (direct-bandgap) monolayer TMD realized on a logic/memory hybrid 3D IC. Left to right, the first four panels show the process flow, the fifth shows an image of the photodetector (PD) array, and the last shows the interconnect wiring. Image adapted with permission from ref. <sup>75</sup>, IEEE.

device schemes for zero-bias operation have been devised<sup>70</sup>. The highest reported responsivity<sup>73</sup> was 0.34 A W<sup>-1</sup>, although the relevant figure of merit for graphene-based photodetectors is the voltage responsivity because graphene detectors are typically based on the photothermoelectric effect (that is, light absorption effectively acts as a voltage source). This implies that the device can be operated without a trans-impedance amplifier as the conversion from voltage to current can be omitted. Although substantial progress has been made in the fabrication of photonics devices in a pilot CMOS foundry environment<sup>74</sup>, current challenges for integration with Si photonics include: the large-area transfer of graphene with mobility of at least a few thousand cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>; appropriate dielectric and encapsulation schemes for low-voltage and hysteresis-free operation; and low-resistance contacting through a 'damascene' process (in which the contact is made by first depositing the dielectric onto the substrate, and subsequently patterning the contact hole which is then filled by metal deposition).

#### Graphene camera for visible and infrared light

Hybrid integration of TMD-based phototransistors with high-density interconnects has been demonstrated in a  $5 \times 5$  pixel array<sup>75</sup> (Fig. 5d). By employing graphene-quantum dot photodetectors, a fully integrated image sensor array of 388 × 288 pixels has been realized by integrating graphene with a CMOS readout integrated circuit<sup>19</sup>, and operation as a digital camera was shown for both visible and infrared light (300-2,000 nm; Fig. 5a, b). This wavelength range is currently not available for any commercial photodetector or image sensor. The integration was based on a BEOL process of graphene onto the Si CMOS die, including a sensitizing layer of PbS colloidal quantum dots that was spin-cast on top of graphene. The functional elements of the CMOS circuitry contained all the trans-impedance amplifiers, compensation resistors and biasing/processing circuits. Despite the high yield of working detector pixels (>98%), the uniformity of the image sensor is expected to improve a great deal in the future by employing a dry-transfer approach. The figures of merit and comparison with competing technology can be found in the supplementary information of ref. <sup>19</sup>, indicating compelling performance characteristics.

Future graphene–CMOS integrated image sensors based on side contacts will increase the active area and improve the contact resistance.

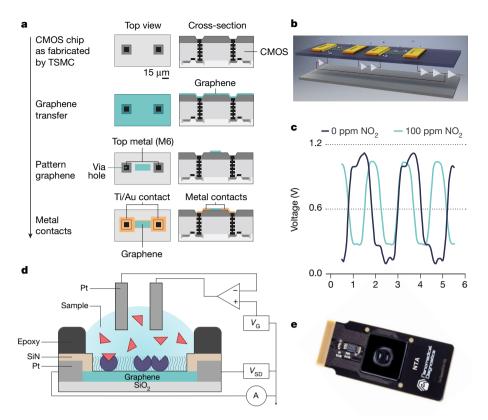

Fig. 6 | Graphene sensors integrated with Si read-out electronics.  $\mathbf{a}$ - $\mathbf{c}$ , A graphene gas sensor.  $\mathbf{a}$ , BEOL process flow for integrating a graphene gas sensor on top of a foundry Si CMOS chip. TSMC, Taiwan Semiconductor Manufacturing Company.  $\mathbf{b}$ , 3D illustration of the monolithic graphene–Si sensor platform, featuring graphene chemiresistor gas sensors (formed as in  $\mathbf{a}$ ) integrated with Si transistors (shown schematically as triangles) to

In general, these advances in BEOL integration of graphene photodetectors with Si CMOS pave the way to the development of 2DM-based image sensors for infrared and terahertz frequencies.

#### Sensors

Contemporary articles provide broad reviews and benchmarking of a wide variety of sensors based on 2DMs<sup>23-25</sup>, and represent an excellent resource for readers interested in sensor science, progress and challenges. From a technology perspective, sensors using 2DMs for gas, chemical and biological detection are straightforward to integrate with Si CMOS technology because only the last layer of the BEOL integration is necessary, which relaxes process and contamination requirements and ensures exposure of the sensor material. A practical 2D-Si sensor chip platform will consist of Si read-out electronics connected through interlayer vias to the top layer of the chip, where graphene or TMDs have been transfer integrated and patterned accordingly to utilize a specific sensor modality. Such an integrated platform was recently demonstrated by Zanjani et al.<sup>20</sup>, where graphene resistance-change devices (chemiresistors) were employed for toxic-gas sensing on top of a foundry Si CMOS chip containing the application-specific read-out circuitry (Fig. 6a-c). Moreover, commercial chips are now available featuring functionalized graphene field-effect bio-sensors (Fig. 6d, e) for selective biomolecular detection with comparable (or superior) performance to conventional devices<sup>28</sup>. Rapid development of commercial 2D-Si sensor platforms is probably imminent as the transfer integration or low-temperature selective growth of suitable 2DMs on Si progresses.

#### Practical matters and integration challenges

There are hundreds of predicted stable layered materials<sup>18,76–78</sup> in a portfolio including semiconductors, semimetals, superconductors, insulators, and the new state of condensed matter known as topological

form a ring-oscillator circuit. **c**, Changes in ring-oscillator frequency and phase in response to a changed concentration of NO<sub>2</sub> gas. **d**, **e**, A graphene bio-sensor. **d**, Illustration of the device structure and read-out circuitry of a graphene field-effect bio-sensor. **e**, Picture of the complete packaged commercial bio-sensor. **a–c**, Images adapted from ref. <sup>20</sup>, Springer Nature; **d**, **e**, images adapted from ref. <sup>28</sup>, Springer Nature.

insulators. To advance these materials for use in integrated 2D-Si CMOS applications, several notable challenges require further research and engineering efforts. (1) Ideally, the growth of single-crystal monolayers needs to be developed. The key step is to control the orientation of each grain during the nucleation or initial growth stage. It is anticipated that a single orientation could lead to a grain-boundary-free layer, which is beneficial for high-performance device applications and uniformity. (2) Nearly wrinkle-free and residue-free benign transfer processes are required. (3) The development of a bottom-up approach to enable the area-selective growth of 2D layers on a CMOS-ready substrate may be another attractive option. To achieve this goal, a location-selective nucleation process compatible with the underlying devices is needed.

#### Wafer-scale growth

Wafer-scale high-quality graphene growth has been reported, and several approaches have been used. To combine fast growth (numerous nucleation points) and large-scale synthesis of single-crystal graphene, one has to rely on the preferential epitaxial organization of the graphene nuclei on the substrate. This has been shown on single-crystal catalytic metallic templates<sup>79–82</sup>, such as Cu <111>, CuNi, Co and Pt, and on semiconducting Ge. Cu/SiO<sub>2</sub>/Si and Ge substrates<sup>83,84</sup>, in particular, offer a wafer-based chemical vapour deposition (CVD) platform compatible with microelectronic processing. For 2D semiconductors, wafer-scale growth of TMDs using various methods—including CVD, metal-organic CVD (MOCVD), ALD and molecular beam epitaxy (MBE)—have also been reported<sup>85–87</sup>. CVD and MOCVD both rely on a nucleation step followed by the TMD lateral growth, a promising route that can be combined with predefined nucleation sites to grow localized single-crystal domains. Submicrometre devices could readily be achieved in a single-crystal domain with a size greater than<sup>87</sup>

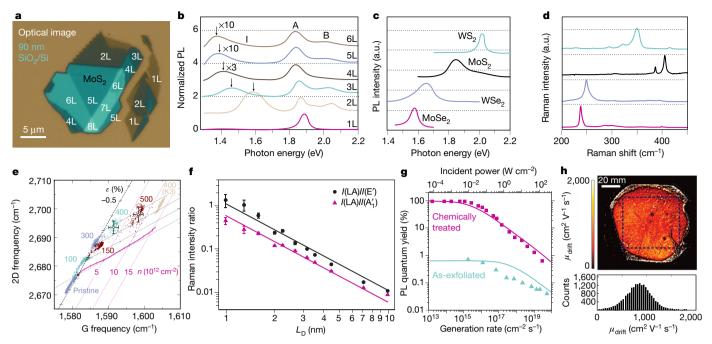

Fig. 7 | Optical characterization of 2DMs suitable for inline metrology. a, Optical colour image of a multi-layer  $MoS_2$  flake on  $SiO_2/Si$ , revealing layer-dependent contrast sufficient for characterization. nL, number of layers. Image adapted from ref.  $^{107}$ , American Chemical Society. b, Normalized layer-dependent photoluminescence (PL) spectra of  $MoS_2$  with three characteristic peaks; A and B are direct bandgap transitions, while I is an indirect transition. Image adapted from ref.  $^{109}$ , American Physical Society. c, d, Characteristic PL and Raman spectra of the four prototypical monolayer semiconducting TMDs. a.u., arbitrary units. e, Correlation between the frequencies of the G and 2D Raman modes of graphene. The green dot represents pristine graphene, with the black dashed line representing the effects of strain ( $\varepsilon$ ) and the red line the effect of carrier density (n). The groups of colours are associated with the anneal temperature from pristine to  $500\,^{\circ}\text{C}$ . Image adapted from ref.  $^{110}$ ,

Springer Nature. f, Dependence of Raman intensity ratios on the average interdefect distance  $(L_{\rm D})$  in monolayer MoS<sub>2</sub>, providing a facile route for characterizing point defects. Error bars represent the standard error from the fitting process. Image adapted from ref. <sup>112</sup>, American Physical Society. g, PL quantum yield as a function of pump power of as-exfoliated and superacid-treated (chemically treated) MoS<sub>2</sub> with much brighter photoluminescence from the (higher-quality) treated sample. Image adapted from ref. <sup>111</sup>, AAAS. h, Main panel, non-contact terahertz-derived charge mobility ( $\mu_{\rm drift}$ ) map of 100-mm-wafer-scale graphene. Side panel, the mobility histogram. Such methods based on the Drude model of terahertz absorption can be broadly applied to 2DMs on insulating or semi-insulating substrates. Image adapted from ref. <sup>114</sup>, Optical Society of America.

$100~\mu m$ . An additional degree of freedom would be the formation of lateral heterojunctions between different TMDs<sup>88,89</sup> or between graphene and a TMD<sup>90</sup>. This could result in a very compelling and flexible method to manufacture 1D junctions at dedicated locations, or to fabricate van der Waals stacks of selected 2DMs<sup>91</sup>.

#### Direct-transfer-free growth methods

Conventional CVD requires a temperature of 900 °C or more to produce good-quality graphene  $^{83,84,92}$ , or 600–900 °C for crystalline TMDs  $^{85,86,93}$ , which hinders direct growth on CMOS-ready wafers with integrated circuits. To avoid the use of transfer processes, which are non-standard in microelectronic production, low-temperature direct growth (at <400–500 °C) of 2DMs are of great interest. On the other hand, direct growth places constraints on temperature, template choice and interface engineering. These constraints have an impact on the achievable material quality.

Plasma- or microwave-assisted CVD has been adopted to activate decomposition of the carbon source, and the growth temperature of graphene can be lowered  $^{94,95}$  to  $400-600\,^{\circ}\mathrm{C}$ . Adding aromatic seeds such as polycyclic hydrocarbons or using certain carbon sources (for example, benzene) can further reduce the CVD growth temperature  $^{96,97}$  to  $<300\,^{\circ}\mathrm{C}$ . Recently, a low barrier has been reported for methane dissolution decomposition in bulk liquid gallium, which can produce graphene on various substrates at a temperature  $^{98}$  of  $50-100\,^{\circ}\mathrm{C}$ .

For TMDs, the growth of  $MoS_2$  single crystals on polyimide substrates at 450 °C has been achieved by simple CVD processes using ammonium molybdate or  $Mo(NMe_2)_4$  as a precursor<sup>99</sup>. Delabie et al. have shown the growth of  $WS_2$  atomic layers with the  $WF_6$  and  $H_2S$  precursors at a low temperature (300–450 °C) using Si or  $H_2$  plasma

as the reducing agent in CVD and ALD, respectively<sup>100</sup>. Although the quality of the obtained 2D layers needs further examination, these low-temperature growth approaches will probably enable the transfer-free integration of desired 2DMs into existing CMOS production technologies for applications where highly crystalline material is not necessary, such as sensors and interconnect stacks. Moreover, 2DMs will need to have a high purity, with metal contamination below 10<sup>11</sup> atoms per square centimetre, for compatibility with silicon cleanroom processing.

#### Scalable clean automated transfer

As mentioned earlier, several options are available to achieve largearea growth of 2DMs at wafer level if template choice and temperature budget are not restricted. During the subsequent transfer, 2DMs will form interfaces with manipulating polymers and transfer media<sup>101</sup>. Residues leading to doping effects, cracks and wrinkles are an unwanted by-product of the mechanical forces involved<sup>102</sup>. The most widely used method is polymer-assisted transfer, where various organic polymers are used as a mechanical support layer to protect and transfer the grown 2D layer. The most challenging step is to completely remove the residual debris and solvent without damaging the film. To avoid this step, direct-transfer methods have been proposed where the 2DM is directly transferred to the target substrate<sup>82,103</sup>.

Arguably, the most promising approach is to combine polymer-assisted transfer with direct transfer, as follows. A layer of 2DM is grown on a polymer substrate. Under vacuum conditions, a movable polymer support is used to pick up a first layer of 2DM from the substrate, and this first layer is then used to directly pick up a second layer, mimicking the small-scale pick-up methods for flake stacking. Such a method has enabled the realization of hetero-stacks of  $MoS_2/WS_2$

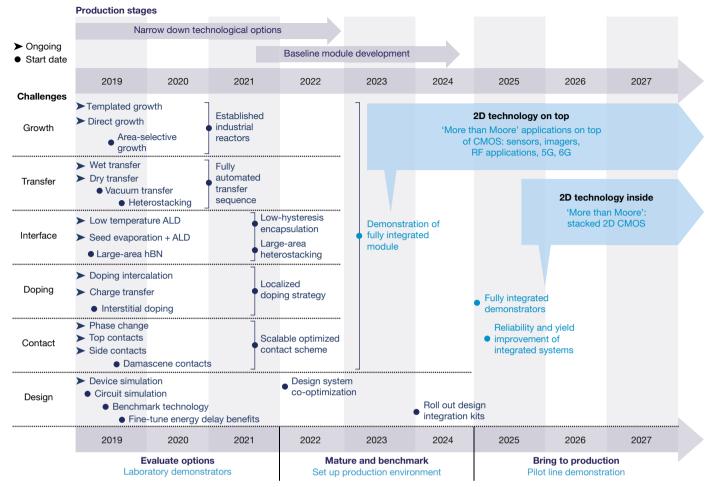

Fig. 8 | Schematic visualization of the technology roadmap for the introduction of 2DMs in CMOS-compatible technology. The effort to introduce 2DMs to enhance the ultra-scaled Si CMOS process ('2D technology inside') requires absolute control of the full integration process, and can only be successful if all the device and integration challenges listed in the left column are resolved. However in the near-term, 2DMs could also be integrated on top of CMOS circuitry mainly for optical input/output, imagers, sensors and radiofrequency applications ('2D technology on top'). These applications will be placed earlier in the

market, as the material and integration requirements are less stringent compared to the needs for CMOS. As soon as automated transfer infrastructure can secure a high-yield transfer, the first 2D devices cointegrated with Si CMOS could be made available for these applications. It is important to make choices in the coming near-term and intensively upscale the growth and transfer processes by building infrastructure that is compliant with the needs and specifications of the CMOS industry. This roadmap has inherent uncertainty and should be interpreted accordingly.

with pristine interlayer interfaces and high spatial uniformity over the wafer scale  $^{104}$ . This hetero-stacking procedure can be extended to diverse 2DMs if the delamination from the growth template is precisely understood and engineered. For example, graphene is easily peeled from Cu without damage after oxidation of the Cu interface. Recently, it was also demonstrated that in so-called electrochemical delamination, it is not the  $\rm H_2$  or  $\rm O_2$  bubbles  $^{105}$  that are generating the delamination force, but an ionic intercalation effect. These studies highlight the importance of adhesion engineering of 2DMs and their growth templates in order to ensure a scalable, clean and automated transfer for building designer hetero-stacks with pristine interfaces at the wafer level.

#### Inline metrology

Methods to rapidly characterize 2DMs at various stages of wafer-scale microelectronic fabrication processes are essential for quality control and industrial adoption of 2D-Si heterogeneous technology. In particular, optical methods are preferred owing to their non-contact simplicity, high-speed wafer mapping and micrometre spatial resolution, and this has led to their widespread adoption in the semiconductor industry. Several non-destructive optical methods have been developed for characterizing layer-dependent properties of different 2DMs (Fig. 7)<sup>106</sup>: (i) optical microscopy on optimized insulating underlayers

offers sufficient contrast for estimating coverage, purity, number of monolayers and uniformity of graphene and TMD films 106,107; (ii) ellipsometry can provide similar information on virtually any application-relevant substrate beyond the substrate restrictions of optical microscopy<sup>108</sup>; and (iii) Raman and photoluminescence (PL) spectroscopy are very powerful in their ability to simultaneously identify a wide variety of 2DMs, and the number and uniformity of the layers<sup>57,106,109</sup>. Moreover, PL can provide a direct measurement of the layer-dependent bandgap for semiconducting TMDs (Fig. 7b). In addition, the width or the intensity of the characteristic peaks in the Raman or PL spectra are indicators of the quality of the film (Fig. 7e-g), which can be correlated with disorder, doping or strain 110-112. Furthermore, advanced optical techniques such as second-harmonic generation can map the strain gradients in noncentrosymmetric 2D layers<sup>113</sup>, and terahertz time-domain spectroscopy can map the electrical properties and mobility of 2DMs on non-conducting substrates (Fig. 7h)<sup>114</sup>. Above all, these methods can be adapted inline in a cleanroom environment in order to monitor the quality of 2D sheets during microfabrication.

#### Device aspects

In existing studies, important device aspects (such as contact resistance, doping and interfaces) have been shown to exhibit large

variability. This variability is partially linked to the fact that most of these devices were processed in laboratory environments, which are focused on innovation rather than on reproducibility. On the other hand, 2DM wafer-level growth and transfer are not as mature as modern Si CMOS processing, which is realized in industrial environments with precision process control. Increased control of the material interface environment will strongly reduce the variability of contact and doping. Localized introduction of molecules offering charge-transfer doping has been demonstrated, but it much reduces the process window for further integration <sup>115</sup>. Encapsulation of 2DMs in a dielectric with fixed charges for remote doping is probably the most CMOScompatible method<sup>44</sup>.

#### Outlook and roadmap

Hetero-integration of specialized components and circuitry for novel computing paradigms (for example, quantum computing and braininspired/neuromorphic computing) with Si CMOS platforms will ensure the pace of steady improvements in computing power as classical scaling fades away. 2DMs are natural candidates for monolithic 3D integration for advanced functionality. Initially specialized components (for example, sensors, imagers, modulators and detectors) that can afford a reduced 2DM performance will enhance the functionality at the last layer of the BEOL. Later on, deeply embedded functionality with 2DM-Si co-optimization could advance emerging computing paradigms that require maximal material performance. However, at the moment, integration of synthetic graphene and 2DMs on Si wafer substrates is lacking production-suitable tools and associated infrastructure<sup>116</sup>, which is holding back reproducible device fabrication and limits the performance compared to record device results achieved with exfoliated hetero-stacked flakes. Only a concerted effort of the research community and the semiconductor industry can overcome the hurdles preventing 2DMs from becoming a heterogeneous complementary technology.

In Fig. 8, we outline a roadmap for 2D device integration with Si CMOS. On the left are listed several generic challenges for 2D integration on CMOS. Initially in the laboratory fundamental properties are explored; in a subsequent phase, the research targets are redefined towards the development of up-scalable options that are found in a real production environment. In the mature and benchmarking phase, tools developed from research knowledge will be introduced in early pilot lines to assess the base steps in initial integration modules. These building blocks will be used for realization of the first circuitry in pilot lines. Finally, functional devices will be demonstrated in in the pilotline phase. During this whole journey from first demonstration towards a product, technological options to meet the different challenges have to be assessed, and choices have to be made when selecting mature options. In Fig. 8 one can see that integration on top of CMOS (represented by the upper device inset) could come earlier to the market as the requirements are less demanding compared to those of 2DMs co-integrated in the BEOL (represented by the lower device inset). These early access technologies will pave the way to deeper integration levels of 2DMs.

As the semiconductor industry is a ubiquitous global business subject to many influences, this roadmap should be interpreted with caution: it covers areas of substantial uncertainty, particularly with respect to the timeline. The route to using 2DMs in future computing systems is via sustained research and development in order to meet the tightly defined requirements of contemporary semiconductor integration.

#### Online content

Any methods, additional references, Nature Research reporting summaries, source data, extended data, supplementary information, acknowledgements, peer review information; details of author contributions and competing interests; and statements of data and code availability are available at https://doi.org/10.1038/s41586-019-1573-9.

Received: 10 November 2018; Accepted: 8 July 2019; Published online 25 September 2019.

- Theis, T. N. & Wong, H. P. The end of Moore's Law: a new beginning for information technology. Comput. Sci. Eng. 19, 41-50 (2017)

- A comprehensive overview of device miniaturization and computing systems, and the developing opportunities at the process, device and architecture levels to advance computing and information technology

- Dennard, R. H., Gaensslen, F. H., Rideout, V. L., Bassous, E. & LeBlanc, A. R. Design of ion-implanted MOSFET's with very small physical dimensions. IEEE J. Solid-State Circuits 9, 256-268 (1974).

- Taur, Y., Wann, C. H. & Frank, D. J. 25nm CMOS design considerations. In *Proc.* IEEE International Electron Devices Meeting (IEDM) 789-792 (IEEE, 1998).

- Thompson, S. et al. A 90 nm logic technology featuring 50nm strained silicon channel transistors, 7 layers of Cu interconnects, low k ILD, and 1 μm<sup>2</sup> SRAM cell. In Proc. 2002 IEEE International Electron Devices Meeting (IEDM) 61-64 (IEEE, 2002).

- Mistry, K. et al. A 45nm logic technology with high-k+metal gate transistors, strained silicon, 9 Cu interconnect layers, 193nm dry pattering, and 100% Pb-free packaging. In Proc. 2007 IEEE International Electron Devices Meeting (IEDM) 247-250 (IEEE, 2007).

- Frank, D. J., Taur, Y. & Wong, H.-S. Generalized scale length for two-dimensional effects in MOSFETs. IEEE Electron Device Lett. 19, 385-387 (1998).

- Yan, R.-H., Ourmazd, A. & Lee, K. F. Scaling the Si MOSFET: from bulk to SOI to bulk. IEEE Trans. Electron Dev. 39, 1704–1710 (1992). Suzuki, K., Tanaka, T., Tosaka, Y., Horie, H. & Arimoto, Y. Scaling theory for

- double-gate SOI MOSFET's. IEEE Trans. Electron Dev. 40, 2326–2329 (1993).

- Auth, C. et al. A 22nm high performance and low-power CMOS technology featuring fully-depleted tri-gate transistors, self-aligned contacts and high density MIM capacitors. In 2012 Symp. on VLSI Technology 131-132 (IEEE, 2012)

- Loubet, N. et al. Stacked nanosheet gate-all-around transistor to enable scaling beyond FinFET. In 2017 Symp. on VLSI Technology T230–T231 (IEEE, 2017).

- English, C. D., Shine, G., Dorgan, V. E., Saraswat, K. C. & Pop, E. Improved contacts to MoS<sub>2</sub> transistors by ultra-high vacuum metal deposition. Nano Lett. 16, 3824-3830 (2016).

- English, C. D., Smithe, K. K., Xu, R. L. & Pop, E. Approaching ballistic transport in monolayer MoS<sub>2</sub> transistors with self-aligned 10 nm top gates. In Proc. 2016 IEEE International Electron Devices Meeting (IEDM) 131–134 (IEEE, 2016).

- Desai, S. B. et al. MoS<sub>2</sub> transistors with 1-nanometer gate lengths. Science 354, 99-102 (2016).

#### An engineering accomplishment reporting a working MoS2 transistor with the gate length defined by a 1-nm carbon nanotube.

- Yang, L. et al. How important is the metal-semiconductor contact for Schottky barrier transistors: a case study on few-layer black phosphorus? ACS Omega 2, 4173-4179 (2017)

- McGuire, F. A. et al. Sustained sub-60 mV/decade switching via the negative capacitance effect in MoS<sub>2</sub> transistors. Nano Lett. 17, 4801-4806 (2017).

- Si, M. et al. Steep-slope hysteresis-free negative capacitance MoS<sub>2</sub> transistors. Nat. Nanotechnol. 13, 24-28 (2018).

- Sabry Aly, M. M. et al. Energy-efficient abundant-data computing: the N3XT 1,000 x. Computer **48**, 24–33 (2015).

- Ferrari, A. C. et al. Science and technology roadmap for graphene, related two-dimensional crystals, and hybrid systems. Nanoscale 7, 4587-5062

- Goossens, S. et al. Broadband image sensor array based on graphene-CMOS integration. Nat. Photon. 11, 366–371 (2017). First report of an integrated

- graphene-Si camera microchip. Mortazavi Zanjani, S. M., Holt, M., Sadeghi, M. M., Rahimi, S. & Akinwande, D. 3D integrated monolayer graphene–Si CMOS RF gas sensor platform. npj 2D Mater. Applicat. 1, 36 (2017).

- Xia, F., Wang, H., Xiao, D., Dubey, M. & Ramasubramaniam, A. Two-dimensional material nanophotonics. *Nat. Photon.* **8**, 899 (2014).

- Sun, Z., Martinez, A. & Wang, F. Optical modulators with 2D layered materials. Nat. Photon. 10, 227-238(2016).

- Joshi, N. et al. A review on chemiresistive room temperature gas sensors based on metal oxide nanostructures, graphene and 2D transition metal dichalcogenides. Mikrochim. Acta 185, 213 (2018).

- Zhu, C., Du, D. & Lin, Y. Graphene-like 2D nanomaterial-based biointerfaces for biosensing applications. Biosens. Bioelectron. 89, 43-55 (2017).

- Wang, Y.-H., Huang, K.-J. & Wu, X. Recent advances in transition-metal dichalcogenides based electrochemical biosensors: a review. Biosens. Bioelectron. 97, 305-316 (2017).

- Huang, L. et al. Graphene/Si CMOS hybrid Hall integrated circuits. Sci. Rep. 4,

- Cheng, C. et al. Monolithic optoelectronic integrated broadband optical receiver with graphene photodetectors. Nanophotonics 6, 1343-1352

- Goldsmith, B. R. et al. Digital biosensing by foundry-fabricated graphene sensors. Sci. Rep. 9, 434 (2019).

- Image Sensors Market https://www.psmarketresearch.com/market-analysis/ image-sensors-market (P&S Intelligence, 2017)

- Koppens, F. H. L. et al. Photodetectors based on graphene, other twodimensional materials and hybrid systems. Nat. Nanotechnol. 9, 780-793(2014).

- NGMN 5G White Paper https://www.ngmn.org/5g-white-paper/5g-whitepaper.html (Next Generation Mobile Networks Alliance, 2015)

- van Uden, R. G. H. et al. Ultra-high-density spatial division multiplexing with a few-mode multicore fibre. Nat. Photon. 8, 865–870 (2014).

- Arakawa, Y., Nakamura, T., Urino, Y. & Fujita, T. Silicon photonics for next generation system integration platform. *IEEE Commun. Mag.* 51, 72–77 (2013)

- Romagnoli, M. et al. Graphene-based integrated photonics for next-generation datacom and telecom. *Nat. Rev. Mater.* 3, 392–414 (2018).

- Fiori, G. et al. Electronics based on two-dimensional materials. Nat. Nanotechnol. 9, 768–779 (2014); erratum 9, 1063 (2014).

- Chhowalla, M., Jena, D. & Zhang, H. Two-dimensional semiconductors for transistors. Nat. Rev. Mater. 1, 16052 (2016).

- 37. Akinwande, D., Petrone, N. & Hone, J. Two-dimensional flexible nanoelectronics. *Nat. Commun.* **5**, 5678 (2014).

- Sarkar, D. et al. A subthermionic tunnel field-effect transistor with an atomically thin channel. *Nature* 526, 91–95 (2015).

- Iannaccone, G., Bonaccorso, F., Colombo, L. & Fiori, G. Quantum engineering of transistors based on 2D materials heterostructures. *Nat. Nanotechnol.* 13, 183–191 (2018); erratum 13, 520 (2018).

# Provides a perspective on the progress in 2D heterostructure transistor devices with benchmarking to Si technology, and the contemporary challenges that need to be addressed for future applications.

- Resta, G. V. et al. Doping-free complementary logic gates enabled by two-dimensional polarity-controllable transistors. ACS Nano 12, 7039–7047 (2018).

- Lee, K., Kulkarni, G. & Zhong, Z. Coulomb blockade in monolayer MoS<sub>2</sub> single electron transistor. *Nanoscale* 8, 7755–7760 (2016).

- Mishra, V. & Salahuddin, S. Intrinsic limits to contact resistivity in transition metal dichalcogenides. *IEEE Electron Device Lett.* 38, 1755–1758 (2017).

- 43. Liu, Y., Duan, X., Huang, Y. & Duan, X. Two-dimensional transistors beyond graphene and TMDCs. *Chem. Soc. Rev.* **47**, 6388–6409 (2018).

- Rai, A. et al. Air stable doping and intrinsic mobility enhancement in monolayer molybdenum disulfide by amorphous titanium suboxide encapsulation. Nano Lett. 15, 4329–4336 (2015).

- Meric, I. et al. Graphene field-effect transistors based on boron-nitride dielectrics. Proc. IEEE 101, 1609–1619 (2013).

Elucidates the properties of hBN and why it is ideal for graphene and, by extension, 2D transistors.

- Teitz, L. & Toroker, M. C. Materials with honeycomb structures for gate dielectrics in two-dimensional field effect transistors – an ab initio study. Ceram. Int. 45, 9339–9347 (2018).

- Yum, J. H. et al. Epitaxial ALD BeO: efficient oxygen diffusion barrier for EOT scaling and reliability improvement. *IEEE Trans. Electron Dev.* 58, 4384–4392 (2011)

- Fuller, S. H. & Millett, L. I. Computing performance: game over or next level? Computer 44, 31–38 (2011).

- Wong, H. S. & Salahuddin, S. Memory leads the way to better computing. Nat. Nanotechnol. 10, 191–194 (2015); erratum 10, 660 (2015).

- Sohn, J., Lee, S., Jiang, Z., Chen, H. & Wong, H. P. Atomically thin graphene plane electrode for 3D RRAM. In *Proc. 2014 IEEE International Electron Devices Meeting (IEDM)* 116–119 (IEEE, 2014).

- Lee, J. et al. Scalable high-performance phase-change memory employing CVD GeBiTe. IEEE Electron Device Lett. 32, 1113–1115 (2011).

- 52. Ahn, C. et al. Energy-efficient phase-change memory with graphene as a thermal barrier. *Nano Lett.* **15**, 6809–6814 (2015).

- Cao, W., Kang, J., Bertolazzi, S., Kis, A. & Banerjee, K. Can 2D-nanocrystals extend the lifetime of floating-gate transistor based nonvolatile memory? *IEEE Trans. Electron Dev.* 61, 3456–3464 (2014).

- Ko, C. et al. Ferroelectrically gated atomically thin transition-metal dichalcogenides as nonvolatile memory. Adv. Mater. 28, 2923–2930 (2016).

- Pan, C. et al. Coexistence of grain-boundaries-assisted bipolar and threshold resistive switching in multilayer hexagonal boron nitride. Adv. Funct. Mater. 27, 1604811 (2017).

- Wu, X. et al. Thinnest nonvolatile memory based on monolayer h-BN. Adv. Mater. 31, 1806790 (2019).

- Ge, R. et al. Atomristor: nonvolatile resistance switching in atomic sheets of transition metal dichalcogenides. Nano Lett. 18, 434–441 (2018).

First report on memory effect in TMD monolayer vertical devices, alluding to a ubiquitous effect in non-metallic TMDs.

- Zhang, F. et al. Electric-field induced structural transition in vertical MoTe<sub>2</sub>- and Mo<sub>1-x</sub>W<sub>x</sub>Te<sub>2</sub>-based resistive memories. Nat. Mater. 18, 55–61 (2019).

- Sangwan, V. K. et al. Gate-tunable memristive phenomena mediated by grain boundaries in single-layer MoS<sub>2</sub>. Nat. Nanotechnol. 10, 403–406 (2015)

- Kshirságar, C. U. et al. Dynamic memory cells using MoS<sub>2</sub> field-effect transistors demonstrating femtoampere leakage currents. ACS Nano 10, 8457–8464 (2016).

- Steinhögl, W., Schindler, G., Steinlesberger, G. & Engelhardt, M. Size-dependent resistivity of metallic wires in the mesoscopic range. *Phys. Rev. B* 66, 075414 (2002).

- Li, L. et al. Vertical and lateral copper transport through graphene layers. ACS Nano 9, 8361–8367 (2015).

- Lee, C.-S., Cline, B., Sinha, S., Yeric, G. & Wong, H.-S. P. 32-bit processor core at 5-nm technology: analysis of transistor and interconnect impact on VLSI system performance. In *Proc.* 2016 IEEE International Electron Devices Meeting (IEDM) 691–694 (IEEE, 2016).

- Lo, C.-L. et al. Studies of two-dimensional h-BN and MoS<sub>2</sub> for potential diffusion barrier application in copper interconnect technology. npj 2D Mater. Applicat. 1, 42 (2017).

- 65. Li, L. et al. BEOL compatible graphene/Cu with improved electromigration lifetime for future interconnects. In *Proc. 2017 IEEE International Electron Devices Meeting (IEDM)* 240–243 (IEEE, 2017).

- Jiang, J. et al. Intercalation doped multilayer-graphene-nanoribbons for next-generation interconnects. *Nano Lett.* 17, 1482–1488 (2017).

- Liu, M., Yin, X. & Zhang, X. Double-layer graphene optical modulator. Nano Lett. 12, 1482–1485 (2012).

- Sorianello, V., Midrio, M. & Romagnoli, M. Design optimization of single and double layer graphene phase modulators in SOI. Opt. Express 23, 6478–6490 (2015).

- Sorianello, V. et al. Graphene–silicon phase modulators with gigahertz bandwidth. Nat. Photon. 12, 40–44 (2018).

- Schuler, S. et al. Controlled generation of a p-n junction in a waveguide integrated graphene photodetector. Nano Lett. 16, 7107-7112 (2016).

- Schall, D. et al. Record high bandwidth integrated graphene photodetectors for communication beyond 180 Gb/s. In Optical Fiber Communication Conf. M2I.4 (Optical Society of America, 2018).

- Lemme, M. C. et al. Gate-activated photoresponse in a graphene p–n junction. Nano Lett. 11, 4134–4137 (2011).

- Shiue, R.-J. et al. High-responsivity graphene-boron nitride photodetector and autocorrelator in a silicon photonic integrated circuit. *Nano Lett.* 15, 7288–7293 (2015).

- Hu, Y. T. et al. Broadband 10Gb/s graphene electro-absorption modulator on silicon for chip-level optical interconnects. In Proc. 2014 IEEE International Electron Devices Meeting (IEDM) 128–131 (IEEE, 2014).

- Yang, C. et al. Enabling monolithic 3D image sensor using large-area monolayer transition metal dichalcogenide and logic/memory hybrid 3D+IC. In Proc. 2016 IEEE Symp. on VI SI Technology 1–2 (IEEE, 2016)

- In Proc. 2016 IEEE Symp. on VLSI Technology 1–2 (IEEE, 2016).

76. Haastrup, S. et al. The computational 2D materials database: high-throughput modeling and discovery of atomically thin crystals. 2D Mater. 5, 042002 (2018).

- Molle, A. et al. Buckled two-dimensional Xene sheets. Nat. Mater. 16, 163–169 (2017).

- Mounet, N. et al. Two-dimensional materials from high-throughput computational exfoliation of experimentally known compounds. *Nat. Nanotechnol.* 13, 246–252 (2018).

## A comprehensive computational study to identify a wider portfolio of diverse 2DMs beyond what is experimentally known.

- Gao, L., Guest, J. R. & Guisinger, N. P. Epitaxial graphene on Cu(111). Nano Lett. 10, 3512–3516 (2010).

- Huang, M. et al. Highly oriented monolayer graphene grown on a Cu/Ni(111) alloy foil. ACS Nano 12, 6117–6127 (2018).

- Ago, H. et al. Epitaxial chemical vapor deposition growth of single-layer graphene over cobalt film crystallized on sapphire. ACS Nano 4, 7407–7414 (2010).

- Verguts, K. et al. Controlling water intercalation is key to a direct graphene transfer. ACS Appl. Mater. Interfaces 9, 37484–37492 (2017).

- Rahimi, S. et al. Toward 300 mm wafer-scalable high-performance polycrystalline chemical vapor deposited graphene transistors. ACS Nano 8, 10471–10479 (2014).

### An engineering achievement, demonstrating the growth of large-area monolayer graphene on industrial-scale 300-mm Si wafers.

- Lee, J.-H. et al. Wafer-scale growth of single-crystal monolayer graphene on reusable hydrogen-terminated germanium. Science 344, 286–289 (2014).

- Choi, W. et al. Recent development of two-dimensional transition metal dichalcogenides and their applications. *Mater. Today* 20, 116–130 (2017).

- Kang, K. et al. High-mobility three-atom-thick semiconducting films with wafer-scale homogeneity. *Nature* 520, 656–660 (2015).

- Zhou, J. et al. A library of atomically thin metal chalcogenides. *Nature* 556, 355–359 (2018).

## A scientific achievement, demonstrating that salt-assisted chemical vapour deposition is a facile method for growing dozens of diverse 2D transitional metal chalcogenides.

- Li, H. et al. Laterally stitched heterostructures of transition metal dichalcogenide: chemical vapor deposition growth on lithographically patterned area. ACS Nano 10, 10516–10523 (2016).

- Xie, S. et al. Coherent, atomically thin transition-metal dichalcogenide superlattices with engineered strain. Science 359, 1131–1136 (2018).

- Guimarães, M. H. D. et al. Atomically thin ohmic edge contacts between two-dimensional materials. ACS Nano 10, 6392–6399 (2016).

- 91. Antonio, R. et al. Scalable synthesis of WS<sub>2</sub> on graphene and h-BN: an all-2D platform for light-matter transduction. *2D Mater.* **3**, 031013 (2016).

- 92. Li, X. et al. Large-area synthesis of high-quality and uniform graphene films on copper foils. *Science* **324**, 1312–1314 (2009).

- Huang, J.-K. et al. Large-area synthesis of highly crystalline WSe<sub>2</sub> monolayers and device applications. ACS Nano 8, 923–930 (2014).

- 94. Boyd, D. A. et al. Single-step deposition of high-mobility graphene at reduced temperatures. *Nat. Commun.* **6**, 6620 (2015)

- 95. Kim, J., Sakakita, H. & Itagaki, H. Low-temperature graphene growth by forced convection of plasma-excited radicals. *Nano Lett.* **19**, 739–746 (2019).

- Lee, E. et al. Heterogeneous solid carbon source-assisted growth of high-quality graphene via CVD at low temperatures. Adv. Funct. Mater. 26, 562–568 (2016).

- 97. Jang, J. et al. Low-temperature-grown continuous graphene films from benzene by chemical vapor deposition at ambient pressure. *Sci. Rep.* **5**, 17955 (2015).

- Fujita, J.-i. et al. Near room temperature chemical vapor deposition of graphene with diluted methane and molten gallium catalyst. Sci. Rep. 7, 12371 (2017).

- Jurca, T. et al. Low-temperature atomic layer deposition of MoS<sub>2</sub> films. Angew. Chem. Int. Ed. 56, 4991–4995 (2017).

- 100. Delabie, A. et al. Low temperature deposition of 2D WS $_2$  layers from WF $_6$  and H $_2$ S precursors: impact of reducing agents. *Chem. Commun.* **51**, 15692–15695 (2015).

- Chen, M., Haddon, R. C., Yan, R. & Bekyarova, E. Advances in transferring chemical vapour deposition graphene: a review. *Mater. Horiz.* 4, 1054–1063 (2017).

- Liang, X. et al. Toward clean and crackless transfer of graphene. ACS Nano 5, 9144–9153 (2011).

- Wang, B. et al. Support-free transfer of ultrasmooth graphene films facilitated by self-assembled monolayers for electronic devices and patterns. ACS Nano 10, 1404–1410 (2016).

- Kang, K. et al. Layer-by-layer assembly of two-dimensional materials into wafer-scale heterostructures. *Nature* 550, 229–233 (2017)

- Verguts, K., Coroa, J., Huyghebaert, C., De Gendt, S. & Brems, S. Graphene delamination using 'electrochemical methods': an ion intercalation effect. Nanoscale 10, 5515–5521 (2018).

- Li, X.-L. et al. Layer-number dependent optical properties of 2D materials and their application for thickness determination. Adv. Funct. Mater. 27, 1604468 (2017).

- Li, H. et al. Rapid and reliable thickness identification of two-dimensional nanosheets using optical microscopy. ACS Nano 7, 10344–10353 (2013).

- Braeuninger-Weimer, P. et al. Fast, noncontact, wafer-scale, atomic layer resolved imaging of two-dimensional materials by ellipsometric contrast micrography. ACS Nano 12, 8555–8563 (2018).

- 109. Mak, K. F., Lee, C., Hone, J., Shan, J. & Heinz, T. F. Atomically thin MoS<sub>2</sub>: a new direct-gap semiconductor. *Phys. Rev. Lett.* **105**, 136805 (2010).

- Lee, J. E., Ahn, G., Shim, J., Lee, Y. S. & Ryu, S. Optical separation of mechanical strain from charge doping in graphene. *Nat. Commun.* 3, 1024 (2012)

- Amani, M. et al. Near-unity photoluminescence quantum yield in MoS<sub>2</sub>. Science 350, 1065–1068 (2015).

- Mignuzzi, S. et al. Effect of disorder on Raman scattering of single-layer MoS<sub>2</sub>. Phys. Rev. B 91, 195411 (2015).

- 113. Mennel, L. et al. Optical imaging of strain in two-dimensional crystals. *Nat. Commun.* **9**, 516 (2018).

- Buron, J. D. et al. Terahertz wafer-scale mobility mapping of graphene on insulating substrates without a gate. Opt. Express 23, 30721–30729 (2015)

- 115. Kiriya, D., Tosun, M., Zhao, P., Kang, J. S. & Javey, A. Air-stable surface charge transfer doping of MoS<sub>2</sub> by benzyl viologen. J. Am. Chem. Soc. 136, 7853–7856 (2014).

- Li, M.-Y., Su, S.-K., Wong, H.-S. P. & Li, L.-J. How 2D semiconductors could extend Moore's law. *Nature* 567, 169–170 (2019).

- 117. The IC memory market will grow 40% to US\$177 billion in 2018. *AnySilicon* https://anysilicon.com/ic-memory-market-will-grow-40-us177-billion-2018/ (Yole Développement, Yole Group of Companies, 2018).

- 118. Auth, C. et al. A 10nm high performance and low-power CMOS technology featuring 3rd generation FinFET transistors, self-aligned quad patterning, contact over active gate and cobalt local interconnects. In Proc. 2017 IEEE International Electron Devices Meeting (IEDM) 673–676 (IEEE, 2017).

- 119. Photonics is about to get flatter. *Photonics Media* https://www.photonics.com/ Articles/Photonics\_is\_About\_to\_get\_Flatter/a55428

- Zuzak, K. et al. Novel hyperspectral imager aids surgeons. SPIE News http:// www.spie.org/news/1394-novel-hyperspectral-imager-aids-surgeons?SSO=1 (SPIE. 2019).

Acknowledgements D.A. acknowledges support from the US National Science Foundation (NSF), the US Office of Naval Research (ONR), and the Presidential Early Career Award for Scientists and Engineers (PECASE) through the US Army Research Office. C.-H.W. and H.-S.P.W. acknowledge support from the NSF, AFOSR MURI, the Semiconductor Research Corporation (SRC) STARnet FAME and SRC JUMP ASCENT, and member companies of the Stanford SystemX Alliance and the Stanford Non-Volatile Memory Technology Research Initiative (NMTRI). L.-J.L. and H.-S.P.W. acknowledge substantial management support from TSMC. C.H. acknowledges support from the Logic Imec Industrial Affiliation Program and funding from the Graphene Flagship initiative. F.H.L.K. acknowledges financial support from the Government of Catalonia through an SGR grant (2017, 1656), from the Spanish Ministry of Economy and Competitiveness through the "Severo Ochoa" Programme for Centres of Excellence in R&D (SEV-2015-0522), from Fundacio Cellex Barcelona, and from the CERCA Programme/Generalitat de Catalunya. Furthermore, the research leading to these results has received funding from the European Union Seventh Framework Programme under grant agreement no. 785219, Graphene Flagship.

**Author contributions** All authors contributed to the writing of this Review, which was led by D.A. and F.H.L.K.

Competing interests The authors declare no competing interests.

#### **Additional information**

**Reprints and permissions information** is available at http://www.nature.com/reprints

**Correspondence and requests for materials** should be addressed to D.A. **Peer review information** *Nature* thanks Jeehwan Kim and Frank Schwierz for their contribution to the peer review of this work.

**Publisher's note** Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

© Springer Nature Limited 2019