# Large-Area Monolayer MoS<sub>2</sub> for Flexible Low-Power RF Nanoelectronics in the GHz Regime

Hsiao-Yu Chang, Maruthi Nagavalli Yogeesh, Rudresh Ghosh, Amritesh Rai, Atresh Sanne, Shixuan Yang, Nanshu Lu, Sanjay Kumar Banerjee, and Deji Akinwande\*

A major contemporary challenge concerns the choice of semiconducting thin-film materials suitable for high-performance field-effect transistors on flexible substrates. Enhanced device performance has been achieved by utilizing conventional semiconductor materials, including crystalline Si and III-V semiconductors; [1-3] however, considering the overall device mechanical flexibility and thickness scalability for high mechanical performance and low operating power,[4] 2D materials have attracted substantial interest in this regard for flexible nanoelectronics. Graphene offers the fastest charge transport (carrier mobility  $\approx 10~000~\text{cm}^2~\text{V}^{-1}~\text{s}^{-1});^{[5-11]}$ however, its lack of a bandgap makes it difficult to turn off (on/off current ratio <10) which is a major drawback for low-power electronics. Alternatively, molybdenum disulfide (MoS<sub>2</sub>), a semiconducting 2D material with sizable bandgaps (≈1.8 eV for monolayer MoS<sub>2</sub> and ≈1.3 eV for bulk MoS<sub>2</sub>)<sup>[12]</sup> can achieve on/off current ratio ≈108, a promising metric for digital electronics. [13] MoS<sub>2</sub> has shown mobilities as high as  $\approx 170$  cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> for few layers, [14] and  $\approx 102$  cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> for monolayer at room temperature, [15] which is comparable to poly-Si, and higher than metal oxide thin film transistors (TFTs).<sup>[4]</sup> The experimental effective velocity ( $v_{eff}$ ) under high-field current saturation region of MoS<sub>2</sub> transistors were reported to be about  $2.8 \times 10^6$  cm s<sup>-1</sup> for few-layer MoS<sub>2</sub>, [16,17] and  $1.1 \times 10^6$  cm s<sup>-1</sup> for monolayer MoS<sub>2</sub>. [18] This range of  $v_{\text{eff}}$  is sufficient to enable GHz speeds at submicron channel lengths, which is not accessible with organic and metal oxide TFTs.[19] The relatively high velocities, when combined with the large bandgap of MoS<sub>2</sub>, make it very attractive for low-power radio-frequency (RF) applications. Moreover, 2D materials possess clear advantages, both in the scalability to ultrathin layer and elastic limit. In comparison with traditional semiconductors for flexible nanoelectronics, 2D materials can afford high electronic performance as well as high mechanical flexibility on arbitrarily large substrates.[4]

Dr. H.-Y. Chang, M. N. Yogeesh, Dr. R. Ghosh, A. Rai, A. Sanne, Prof. S. K. Banerjee, Prof. D. Akinwande Microelectronics Research Center The University of Texas at Austin Austin, TX 78758, USA E-mail: deji@ece.utexas.edu

S. Yang, Prof. N. Lu

Department of Aerospace Engineering and Engineering Mechanics The University of Texas at Austin Austin, TX 78712, USA

DOI: 10.1002/adma.201504309

We note that for RF circuits, effective saturation velocity rather than mobility is usually the relevant device metric due to the high terminal electric fields.<sup>[4]</sup> Previous studies have revealed the potential of few-layer exfoliated MoS2 on SiO2/Si substrate that achieved a transit frequency,  $f_T$ , of 42 GHz at a gate length of 68 nm (13.5 GHz for similar device on flexible substrate):<sup>[14]</sup> however, the exfoliation process is not scalable for practical or large-area applications. Very recently, monolayer MoS<sub>2</sub> grown by chemical vapor deposition (CVD) has been shown to achieve an  $f_T$  of 6.7 GHz at a gate length of 250 nm on rigid substrates.<sup>[18]</sup> In this work, we demonstrate the first RF performance for MoS<sub>2</sub> field-effect transistors (FETs) on flexible substrates based on CVD-grown monolayers, featuring record GHz cutoff frequency and effective saturation velocity. Our result suggests that CVD-grown MoS2 is suitable for high-frequency operation in large-area flexible nanoelectronic applications.

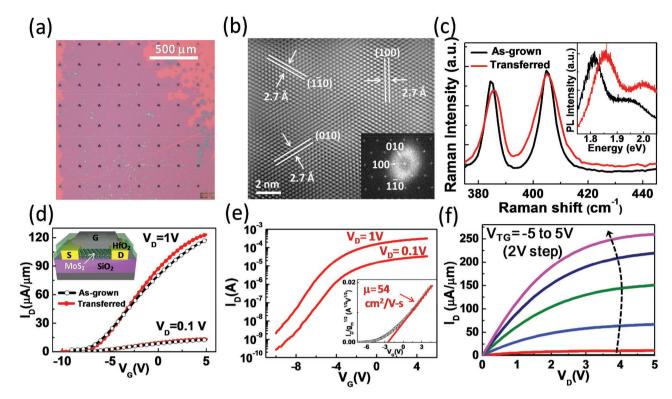

Large-area (millimeter-scale) monolayer MoS2, the prototypical transitional-metal dichalcogenide (TMD) was grown by CVD on SiO<sub>2</sub>/Si (Figure 1a). Figure 1b shows the transmission electron microscopy (TEM) image of monolayer CVD MoS2 with lattice spacing of 0.27 nm confirming the as-grown material quality. Poly(methyl methacrylate) (PMMA) supported wet transfer process was used to transfer MoS<sub>2</sub> to various substrates, including SiO<sub>2</sub>/Si and polyimide (PI). (The detailed information about the CVD-growth, uniformity of the CVD-grown MoS<sub>2</sub> film, and the transfer process can be found in Figure S1 and S2 in the Supporting Information). Figure 1c shows the comparison between the transferred and the as-grown MoS2 samples from Raman and photoluminescence (PL) spectrum. A blue shift of the  $\rm E^{1}_{2g}$  peak in the Raman spectra ( $\approx 1.0~cm^{-1}$ ) and the optical bandgap (≈45 meV) in the photoluminescence spectra are observed after transfer. It was reported by Conley et al. that with increased tensile strain, the  $E^1_{2g}$  peak in Raman spectra shows phonon softening and photoluminescence shows bandgap reduction.<sup>[20,21]</sup> Our results suggest that there is a release of tensile strain (<1%) after transfer that can be attributed to the high-temperature CVD-growth process which induces residual tensile strain in the as-grown sample. Our observation is in agreement with similar trends as reported previously.<sup>[22]</sup> Moreover, the Raman and PL spectra also confirm the preserved quality of MoS<sub>2</sub> after the transfer process.

CVD-MoS<sub>2</sub> devices on SiO<sub>2</sub>/Si were evaluated under ambient conditions for the initial investigation of the electronic performance of monolayer MoS<sub>2</sub>. A schematic of the top-gate device structure with overlap between S/D and gate is shown in the inset in Figure 1d (the optical image and the mask design can be found in Figure S5 in the Supporting Information).

Figure 1. a) Optical image of mm-scale monolayer. b) FFT-filtered TEM image of monolayer CVD MoS₂ with lattice spacing of 0.27 nm and the inset is the corresponding FFT showing the spots that were used in the filter. c) Raman and photoluminescence (inset) spectrum before and after transfer confirming the preserved quality. d)  $I_D$ – $V_G$  characteristics are shown in linear scale. A comparison between the as-grown CVD MoS₂ FET and the transferred sample ( $L_g$  = 1 μm) on SiO₂/Si confirming that the transfer process used in our process does not degrade the performance. Inset is a schematic of the top gate device structure with overlap between source/drain and gate. e) Transferred CVD-grown MoS₂ FET.  $I_D$ – $V_G$  with ON/OFF ratio ≥10<sup>5</sup> and  $\mu_o \approx 54$  cm² V<sup>-1</sup> s<sup>-1</sup> based on the Y-function ( $I_D$ / $V_g$ m) method (inset) that excludes  $R_c$ .  $I_D$  μm,  $I_D$  Transferred CVD-grown MoS₂ FET.  $I_D$ – $I_D$  Characteristics in linear scale shows good saturation. High saturation current ( $I_{sat}$ ) density ≈250 μA μm<sup>-1</sup> is achieved.

To verify the effect of the wet transfer used in our process, the transfer  $(I_D-V_G)$  characteristics of the as-grown and the transferred MoS2 FET on SiO2/Si are compared in the linear scale, as shown in Figure 1d. The comparison confirms that the wet transfer used in our process does not degrade the electronic performance. Representative  $I_D$ – $V_G$  characteristics of the transferred MoS<sub>2</sub> FET are shown in Figure 1e. The switching ratio  $(I_{\rm on}/I_{\rm off})$  is greater than  $10^5$ . A low-field mobility  $(\mu_{\rm o})$  of 54 cm² V<sup>-1</sup> s<sup>-1</sup> and an  $R_c$  of 2.7 k $\Omega$   $\mu m$  are extracted based on the Y-function  $(I_{\rm D}/\sqrt{g_{\rm m}})$  method.[23,24] Figure 1f represents the output characteristics  $(I_D-V_D)$  showing good current saturation with an ON-current of about 250 µA µm<sup>-1</sup>. The enhanced device performance can be attributed to the high-k doping effect of the gate dielectric on the MoS2 channel, wherein, the HfO2 dopes the MoS2 owing to its interfacial oxygen vacancies.[25] These device characteristics represent the state-of-theart for CVD-grown monolayer MoS<sub>2</sub> FETs. Table S1 (Supporting Information) summarizes the device performance of previously reported CVD-grown  $MoS_2$ . [18,26–30]

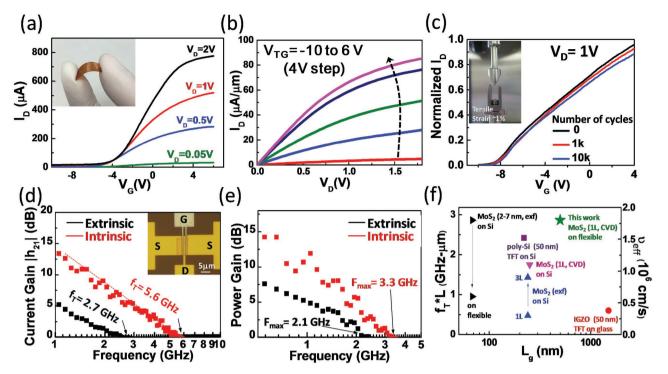

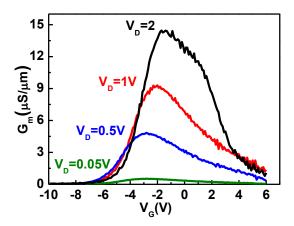

Similar fabrication process was applied for top-gated dual-finger RF TFTs with gate-source/drain underlap to minimize the parasitic capacitance at high frequencies ( $L_{\rm g}=500$  nm,  $W=9~\mu{\rm m}$  for each finger and the total width = 18  $\mu{\rm m}$ ). The optical image and the mask design can be found in Figure S5 in the Supporting Information. Figure 2a,b shows the  $I_{\rm D}-V_{\rm G}$  and  $I_{\rm D}-V_{\rm D}$  characteristics of the transferred CVD-grown MoS<sub>2</sub>

FETs on flexible PI substrate, respectively.  $\mu_0 = 22 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ and  $R_c = 9.4 \text{ k}\Omega$  µm are extracted from the Y-function method (more information about the  $G_{\rm m}$ , and mobility extraction from different devices can be found in Figure S6 and S7 in the Supporting Information). The saturation current ( $I_{sat}$ ) is about 85 μA μm<sup>-1</sup>, an order of magnitude higher than our previous result on flexible exfoliated MoS<sub>2</sub>.<sup>[31]</sup> The increase of the contact resistance in this case, however, is due to the underlap design resulting in ungated source/drain access regions. Table 1 summarizes the performance of contemporary flexible MoS<sub>2</sub> FETs including both CVD-grown and exfoliated devices.[31-36] It is noted that mobility can be improved by increasing the layers of MoS2, and a degradation of mobility is often found while converting the substrate from rigid to flexible substrate with a similar fabrication process, which can be attributed to the increased surface roughness and poor thermal conductivity of common flexible substrates. [14,35] Multicycle three-point mechanical bending experiments demonstrate the robustness of our flexible MoS2 device. As shown in Figure 2c, RSA-G2 dynamic mechanical analyzer (DMA) with three-point bending fixture is used for repeated bending up to 10 000 cycles. The devices were at the center of curvature of the substrate for the bending experiments. A tensile strain of 1% was applied during the multicycle bending test. The transfer characteristics of flexible MoS2 transistors reveal a strong stability even after 10 000 cycles of bending (more information about the

www.advmat.de

Figure 2. a) Electrical characteristics of flexible MoS₂ FETs ( $L_g = 500$  nm) at 300 K. Inset is an optical image of the flexible sample. b)  $I_D$ – $V_D$  characteristics indicate negligible Schottky barrier in the linear region, and current saturation at high fields. Drain current achieves ≈85 μA μm<sup>-1</sup>, which is an order of magnitude higher than our previous result on exfoliated MoS₂. [31] c) A tensile strain of 1% was applied during the multicycle bending test. The transfer characteristics of the flexible MoS₂ transistors demonstrate strong stability even after 10 000 cycles of bending. Inset is the optical image of the three-point bending fixture. d) Intrinsic  $f_T \approx 5.6$  GHz was achieved. Device width is 18 μm. The gate bias is at peak  $G_m$  and  $V_D = 2$  V. Inset is an optical image of the RF TFT. e) The power gain (U) versus frequency. The power gain considered is the unilateral power gain. Operating at the same DC bias point, an intrinsic  $f_{max}$  of 3.3 GHz was extracted. f) RF TFT performance benchmarking to prior MoS₂ FETs and similar inorganic TFTs (<100 nm film thickness). The comparison indicates our  $f_TL$  and  $ν_{eff}$  are the highest on flexible substrates and similar to the highest exfoliated MoS₂ values on rigid substrate. Data taken from ref. [14] (right triangles), ref. [39] (square), ref. [18] (down triangle), ref. [40] (up triangles), and ref. [19] (circle).

strain-dependent DC performance can be found in Figure S8 in the Supporting Information).

We investigated the high-frequency properties of flexible CVD MoS<sub>2</sub> TFTs based on two well established RF performance metrics; the unity current gain and unity power gain cutoff frequencies. The frequency where the current gain is unity is called the transit frequency ( $f_T$ ) and, similarly, where the power gain becomes unity is called the maximum oscillation frequency ( $f_{max}$ ).<sup>[37]</sup> S-parameter measurements were conducted to determine the  $f_T$  and  $f_{max}$  using an Agilent Vector Network

Table 1. Summary of contemporary flexible  $MoS_2$  thin-film transistors.

| Max mobility<br>[cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> ] | <i>L</i> <sub>g</sub><br>[μm] | MoS <sub>2</sub> | Substrate | Reference |  |

|--------------------------------------------------------------------|-------------------------------|------------------|-----------|-----------|--|

| 22 <sup>a)</sup>                                                   | 0.5                           | CVD, 1L          | PI        | This work |  |

| 19 <sup>a)</sup>                                                   | 0.5                           | CVD, 1L          | PI        | [32]      |  |

| 3                                                                  | 480                           | CVD, 3L          | PI        | [33]      |  |

| 30 <sup>a)</sup>                                                   | 1                             | Exf, ≈10 nm      | PI        | [31]      |  |

| 19 <sup>a)</sup>                                                   | 4.3                           | Exf, ≈3.5 nm     | PI        | [34]      |  |

| 29                                                                 | 1                             | Exf, 3L          | PEN       | [35]      |  |

| 8                                                                  | 4                             | Exf, ≈58 nm      | PET       | [36]      |  |

<sup>&</sup>lt;sup>a)</sup>Mobility excludes  $R_c$ . Exfoliation (Exf); layer (L).

Analyzer (VNA-E8361C) and cascade electrical probe station. The high-frequency measurement results are illustrated in Figure 2d,e as current gain  $(h_{21})$  and power gain (U), respectively. The power gain considered is the unilateral power gain. For maximum charge transport, the MoS<sub>2</sub> RF TFT was biased at the peak  $G_{\rm m}$  where  $V_{\rm G} = -1~{\rm V}$  and  $V_{\rm D} = 2~{\rm V}$ , yielding an extrinsic  $f_{\rm T} \approx 2.7$  GHz and  $f_{\rm max} \approx 2.1$  GHz. Subsequently, standard RF deembedding was conducted using identical OPEN and SHORT structures[8,38] to de-embed the effect of parasitic capacitances and resistances in the device structure, and extract the intrinsic monolayer CVD MoS<sub>2</sub> RF performance metrics:  $f_T \approx 5.6$  GHz and  $f_{\text{max}} \approx 3.3$  GHz. Alternatively, another metric to evaluate the speed performance of RF TFTs is the effective saturation velocity. [4] Analytically,  $f_T = v_{\text{eff}}/2\pi L$  under high-field conditions that yield maximum transport. In this regime,  $v_{\text{sat}}$  can be estimated from the measured  $f_T$  L<sup>-1</sup>. As shown in Figure 2f, our MoS<sub>2</sub> RF TFTs afford  $f_{\rm T}$  L<sup>-1</sup> ( $\nu_{\rm eff}$ ) of 2.8 GHz  $\mu m^{-1}$  (1.8  $\times$  10<sup>6</sup> cm s<sup>-1</sup>) which is similar to the best exfoliated MoS2 values on rigid substrates and higher than previously reported flexible MoS2 and other inorganic TFTs with sub-100 nm thickness.[14,18,19,39,40]

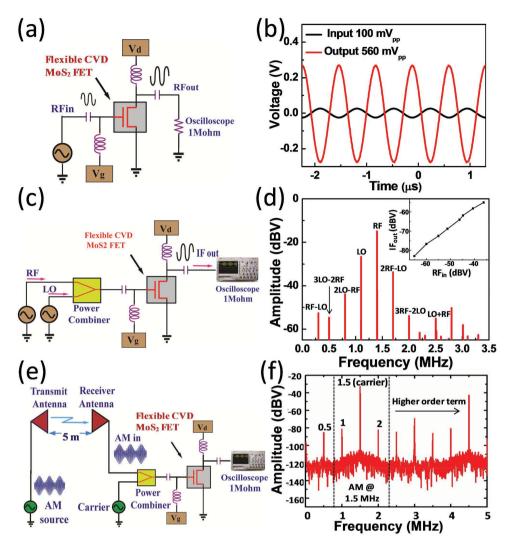

Having obtained good mobility, drain-current saturation and  $f_{\rm T}$  and  $f_{\rm max}$  in the GHz range, flexible CVD MoS<sub>2</sub> amplifier and mixer circuits, the basic building blocks of RF systems, were fabricated and demonstrated for the first time. A flexible MoS<sub>2</sub> common source (CS) amplifier ( $L_{\rm g}=0.5~\mu{\rm m},~W=18~\mu{\rm m}$ ) is

Figure 3. a) Circuit schematic of common-source amplifier based on MoS<sub>2</sub> flexible TFT ( $f_{RF} \approx 1.4$  MHz). b) Input and output voltage waveforms of CS amplifier showing 15 dB gain. c) Circuit schematic of MoS<sub>2</sub> FET-based RF mixer ( $f_{RF} \approx 1.4$  MHz,  $f_{LO} \approx 1.1$  MHz,  $f_{LO} \approx 3.0$  kHz). d) Output frequency spectrum of the mixer. The inset shows the conversion gain of the mixer is ca. –17 dB. e) Circuit schematic of MoS<sub>2</sub> FET-based wireless AM receiver. The distance between transmit and receiver antenna is 5 m, and the carrier frequency ( $ω_C$ ) is 1.5 MHz. f) AM receiver output spectrum showing clearly demodulated signal at 500 kHz.

shown in **Figure 3**a. The TFT is biased at the peak  $G_{\rm m}$  point ( $V_{\rm G}=-1$  V,  $V_{\rm D}=2$  V). The RF input ( $f_{\rm in}\approx 1.4$  MHz) is provided by an Agilent signal generator and fed to the gate input of the TFT. The output of the TFT is connected to an oscilloscope (load resistance = 1 M $\Omega$ ) and affords a gain of 15 dB at 1.4 MHz as shown in Figure 3b. In this work, the amplifier operating frequency is limited by the measurement setup. Further research is necessary to realize matched input and output impedance networks for resonant or broadband GHz operation.

In addition, a single transistor active mixer using flexible CVD  $MoS_2$  FET was developed as shown in Figure 3c. In this design, we operate the FET in the nonlinear region of its output characteristics ( $I_D \sim V_G^n$ , where n is  $\approx 1.5-2$  in FETs) for nonlinear signal processing such as frequency translation or mixing. The RF input ( $f_{RF} \approx 1.4$  MHz) is power combined with a local oscillator ( $f_{LO} \approx 1.1$  MHz) and fed to the gate input of the mixer. The output of the nonlinear mixer typically contains all the generated

harmonics. It is low-pass filtered to obtain the intermediate frequency signal ( $f_{\rm IF} = f_{\rm RF} - f_{\rm LO}$ ). This IF output signal is measured using an oscilloscope and the frequency spectrum is displayed in Figure 3d. Equation S1–S5 in the Supporting Information describes mathematically the operation of this nonlinear mixer. The inset of Figure 3d shows the linearity of the mixer ( $IF_{\rm out}$  power vs  $RF_{\rm in}$  power) offering a maximum conversion gain of -17 dB. By improving the layout design, reducing parasitic capacitance and contact resistance, the conversion gain is expected to improve significantly, potentially affording positive gains.

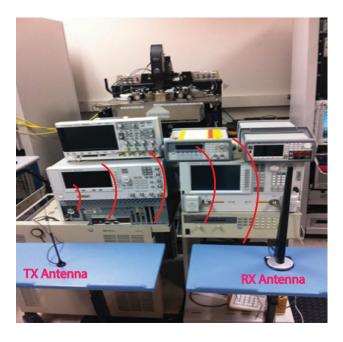

We also demonstrate for the first time wireless amplitude modulation (AM) receiver using the flexible CVD MoS<sub>2</sub> RF FET. The schematic of the receiver is shown in Figure 3e. AM signal is generated by an Agilent signal generator with modulating frequency ( $\omega_{\rm m}$ ) = 500 kHz, carrier frequency ( $\omega_{\rm C}$ ) = 1.5 MHz, and the depth of modulation = 50%. The wireless communication distance between the transmit and receive antenna is 5 m. The

ADVANCED MATERIALS

/ww.advmat.de

received signal is combined with the carrier frequency through a power combiner, and fed to the gate input of the MoS<sub>2</sub> RF FET. Our flexible CVD MoS<sub>2</sub> FET performs analog signal processing by multiplying the carrier and modulating signals received from the antenna resulting in demodulated and harmonic signals at the transistor output as shown in Figure 3f. The detailed information about the measurement setup and the working principle are described in the Supporting Information (Figure S9).

In conclusion, flexible CVD-grown MoS2 TFTs were demonstrated to be suitable for high-frequency operation. Our studies yield the highest performance for CVD-grown monolayer MoS<sub>2</sub> device properties on flexible substrates to date. Intrinsic transit frequencies of 5.6 GHz and maximum oscillation frequencies of 3.3 GHz have been achieved. The radio frequency performance of our device corresponds to  $f_T L_p$  of  $\approx 2.8$  GHz  $\mu m$ , and  $v_{\rm eff}$  of  $\approx 1.8 \times 10^6$  cm s<sup>-1</sup> which are comparable to the best results obtained utilizing exfoliated multilayer MoS2 on rigid substrates. Furthermore, multicycle three-point bending results demonstrated the electrical robustness of our flexible MoS<sub>2</sub> transistors after 10 000 cycles of mechanical bending. Additionally, basic RF circuit building blocks such as amplifier, mixer, and wireless AM receiver have been demonstrated. These collective results indicate that MoS2 can serve as a suitable semiconducting material for low-power, high-frequency devices for large-area flexible nanoelectronics and smart nanosystems owing to its unique combination of large bandgap, high effective saturation velocity, and high mechanical strength.

#### **Experimental Section**

Device Fabrication: For the devices made on Si, degenerately doped Si substrate was used as the bottom gate, and 270 nm  $SiO_2$  grown by thermal oxidation was used as the gate dielectric. CVD  $MoS_2$  was transferred (the detailed information about the CVD-growth and the transfer process can be found in Figure S1 and S2 in the Supporting Information). The active region was defined by electron beam lithography, followed by a dry etching process ( $Cl_2$ , 75 W, 1 min). Ag/Au (20/20 nm) deposited by electron beam evaporation was used as the source/drain electrode, and  $HfO_2$  (30 nm) was deposited at 200 °C by the atomic layer deposition (ALD) method as the top gate dielectric. Pd (40 nm) deposited by electron beam evaporation was used as the top gate.

For the flexible devices, we used commercially available polyimide (Kapton) with a thickness of 125  $\mu m$  as the flexible substrate, and spin-coated an additional liquid polyimide film (PI-2574 from HD Micro Systems) on the surface with a thickness of 13  $\mu m$  to reduce the surface roughness. The liquid polyimide was cured at 300 °C for 1 h. The same spin-coating/curing process was repeated again on the opposite side in order to balance the residual strain induced by the curing process. HfO $_2$  (30 nm) was deposited at 200 °C by ALD on the bare PI for subsequent device fabrication.

#### **Supporting Information**

Supporting Information is available from the Wiley Online Library or from the author.

#### Acknowledgements

H.-Y.C. and M.N.Y. contributed equally to this work. The authors would like to thank Hema C. P. Movva for sharing the experience of the transfer method, and Harry Chou for the discussion about the

time-of-flight secondary-ion mass spectrometry (ToF-SIMS). R.G. would like to thank Dr. Di Wu from UT Austin, Department of Physics. This work was supported, in part, by the Office of Naval Research (ONR) under contract no. N00014-1110190, the Army Research Office (ARO) under STTR award number W911NF-14-P-0030, and the NSF NASCENT Engineering Research Center under Cooperative Agreement No. EEC-1160494. Fabrication was conducted at the Microelectronics Research Center at the University of Texas at Austin.

Received: September 2, 2015 Revised: October 31, 2015 Published online:

- C. Wang, J. C. Chien, H. Fang, K. Takei, J. Nah, E. Plis, S. Krishna, A. M. Niknejad, A. Javey, *Nano Lett.* 2012, 12, 4140.

- [2] H. Zhou, J. H. Seo, D. M. Paskiewicz, Y. Zhu, G. K. Celler, P. M. Voyles, W. Zhou, M. G. Lagally, Z. Ma, Sci. Rep. 2013, 3, 1291.

- [3] C. Yoon, G. Cho, S. Kim, IEEE Trans. Electron Devices, 2011, 58, 1096.

- [4] D. Akinwande, N. Petrone, J. Hone, Nat. Commun. 2014, 5, 5678.

- [5] A. K. Geim, K. S. Novoselov, Nat. Mater. 2007, 6, 183.

- [6] N. Petrone, C. R. Dean, I. Meric, A. M. van der Zande, P. Y. Huang, L. Wang, D. Muller, K. L. Shepard, J. Hone, *Nano Lett.* 2012, 12, 2751.

- [7] N. Petrone, I. Meric, J. Hone, K. L. Shepard, Nano Lett. 2012, 13, 121.

- [8] Y. M. Lin, C. Dimitrakopoulos, K. A. Jenkins, D. B. Farmer, H. Y. Chiu, A. Grill, P. Avouris, Science 2010, 327, 662.

- [9] M. E. Ramón, K. N. Parrish, S. F. Chowdhury, C. W. Magnuson, H. C. P. Movva, R. S. Ruoff, S. K. Banerjee, D. Akinwande, *IEEE Trans. Nanotechnol.* 2012, 11, 877.

- [10] J. Lee, K. N. Parrish, S. F. Chowdhury, T.-J. Ha, Y. Hao, L. Tao, A. Dodabalapur, R. S. Ruoff, D. Akinwande, presented at *IEEE Int. Electron Devices Meeting (IEDM)*, San Francisco, CA, USA, December 2012.

- [11] L. Tao, J. Lee, H. Li, R. D. Piner, R. S. Ruoff, D. Akinwande, Applied Phys. Lett. 2013, 103, 183115.

- [12] S. Han, H. Kwon, S. K. Kim, S. Ryu, W. S. Yun, D. Kim, J. Hwang, J.-S. Kang, J. Baik, H. Shin, Phys. Rev. B 2011, 84, 045409.

- [13] B. Radisavljevic, A. Radenovic, J. Brivio, V. Giacometti, A. Kis, Nat. Nanotechnol. 2011, 6, 147.

- [14] R. Cheng, S. Jiang, Y. Chen, Y. Liu, N. Weiss, H. C. Cheng, H. Wu, Y. Huang, X. Duan, *Nat. Commun.* 2014, 5, 5143.

- [15] A. Rai, A. Valsaraj, H. C. P. Movva, A. Roy, R. Ghosh, S. Sonde, S. Kang, J. Chang, T. Trivedi, R. Dey, S. Guchhait, S. Larentis, L. F. Register, E. Tutuc, S. K. Banerjee, *Nano Lett.* 2015, 15, 4329.

- [16] G. Fiori, B. N. Szafranek, G. Iannaccone, D. Neumaier, Appl. Phys. Lett. 2013, 103, 233509.

- [17] X. Zou, J. Wang, C. H. Chiu, Y. Wu, X. Xiao, C. Jiang, W. W. Wu, L. Mai, T. Chen, J. Li, Adv. Mater. 2014, 26, 6255.

- [18] A. Sanne, R. Ghosh, A. Rai, M. N. Yogeesh, S. H. Shin, A. Sharma, K. Jarvis, L. Mathew, R. Rao, D. Akinwande, S. Banerjee, *Nano Lett.* 2015, 15, 5309.

- [19] L.-Y. Su, J. Huang, Solid-State Electron. 2015, 104, 122.

- [20] H. J. Conley, B. Wang, J. I. Ziegler, R. F. Haglund, Jr., S. T. Pantelides, K. I. Bolotin, *Nano Lett.* **2013**, *13*, 3626.

- [21] C. Rice, R. Young, R. Zan, U. Bangert, D. Wolverson, T. Georgiou, R. Jalil, K. Novoselov, *Phys. Rev. B* **2013**, *87*, 081307.

- [22] M. Amani, M. L. Chin, A. L. Mazzoni, R. A. Burke, S. Najmaei, P. M. Ajayan, J. Lou, M. Dubey, Appl. Phys. Lett. 2014, 104, 203506.

- [23] G. Ghibaudo, Electron. Lett. 1988, 24, 543.

- [24] H. Y. Chang, W. N. Zhu, D. Akinwande, Appl. Phys. Lett. 2014, 104, 113504.

www.advmat.de

www.MaterialsViews.com

- [25] A. Rai, A. Valsaraj, H. C. P. Movva, A. Roy, E. Tutuc, L. F. Register, S. K. Banerjee, presented at *Device Research Conf. (DRC)*, Columbus, OH, USA, June 2015.

- [26] R. Kappera, D. Voiry, S. E. Yalcin, W. Jen, M. Acerce, S. Torrel, B. Branch, S. Lei, W. Chen, S. Najmaei, APL Mater. 2014, 2, 092516.

- [27] L. Yu, Y.-H. Lee, X. Ling, E. J. Santos, Y. C. Shin, Y. Lin, M. Dubey, E. Kaxiras, J. Kong, H. Wang, *Nano Lett.* 2014, 14, 3055.

- [28] H. Schmidt, S. Wang, L. Chu, M. Toh, R. Kumar, W. Zhao, A. H. Castro Neto, J. Martin, S. Adam, B. Özyilmaz, *Nano Lett.* 2014, 14, 1909.

- [29] H. Liu, M. Si, S. Najmaei, A. T. Neal, Y. Du, P. M. Ajayan, J. Lou, P. D. Ye, Nano Lett. 2013, 13, 2640.

- [30] H. Wang, L. Yu, Y. Lee, W. Fang, A. Hsu, P. Herring, M. Chin, M. Dubey, L. Li, J. Kong, T. Palacios, presented at 2012 IEEE Int. Electron Devices Meeting (IEDM), San Francisco, CA, USA, December 2012.

- [31] H. Y. Chang, S. Yang, J. Lee, L. Tao, W. S. Hwang, D. Jena, N. Lu, D. Akinwande, ACS Nano 2013, 7, 5446.

- [32] M. Amani, R. A. Burke, R. M. Proie, M. Dubey, Nanotechnology 2015, 26, 115202.

- [33] J. Pu, Y. Yomogida, K. K. Liu, L. J. Li, Y. Iwasa, T. Takenobu, *Nano Lett.* 2012, 12, 4013.

- [34] G. A. Salvatore, N. Munzenrieder, C. Barraud, L. Petti, C. Zysset, L. Buthe, K. Ensslin, G. Troster, ACS Nano 2013, 7, 8809.

- [35] G.-H. Lee, Y.-J. Yu, X. Cui, N. Petrone, C.-H. Lee, M. S. Choi, D.-Y. Lee, C. Lee, W. J. Yoo, K. Watanabe, ACS Nano 2013, 7, 7931.

- [36] J. Yoon, W. Park, G. Y. Bae, Y. Kim, H. S. Jang, Y. Hyun, S. K. Lim, Y. H. Kahng, W. K. Hong, B. H. Lee, H. C. Ko, Small 2013, 9, 3295.

- [37] F. Schwierz, Proc. IEEE 2013, 101, 1567.

- [38] J. Lee, T.-J. Ha, H. Li, K. N. Parrish, M. Holt, A. Dodabalapur, R. S. Ruoff, D. Akinwande, ACS Nano 2013, 7, 7744.

- [39] K.-M. Chen, T.-I. Tsai, T.-Y. Lin, H.-C. Lin, T.-S. Chao, G.-W. Huang, T.-Y. Huang, Electron Device Lett., IEEE 2013, 34, 1020.

- [40] D. Krasnozhon, D. Lembke, C. Nyffeler, Y. Leblebici, A. Kis, Nano Lett. 2014, 14, 5905.

6

# ADVANCED MATERIALS

## **Supporting Information**

for Adv. Mater., DOI: 10.1002/adma.201504309

Large-Area Monolayer MoS<sub>2</sub> for Flexible Low-Power RF Nanoelectronics in the GHz Regime

Hsiao-Yu Chang, Maruthi Nagavalli Yogeesh, Rudresh Ghosh, Amritesh Rai, Atresh Sanne, Shixuan Yang, Nanshu Lu, Sanjay Kumar Banerjee, and Deji Akinwande\* Copyright WILEY-VCH Verlag GmbH & Co. KGaA, 69469 Weinheim, Germany, 2013.

### **Supporting Information**

Title Large-area monolayer MoS<sub>2</sub> for flexible low-power RF nanoelectronics in the

GHz regime

Hsiao-Yu Chang, \* Maruthi Nagavalli Yogeesh, \* Rudresh Ghosh, Amritesh Rai, Atresh Sanne, Shixuan Yang, Nanshu Lu, Sanjay Kumar Banerjee, and Deji Akinwande\*

Hsiao-Yu Chang<sup>[+]</sup>, Maruthi Nagavalli Yogeesh<sup>[+]</sup>, Dr. Rudresh Ghosh, Amritesh Rai, Atresh Sanne, Prof. Sanjay Kumar Banerjee, Prof. Deji Akinwande, Microelectronics Research Center, The University of Texas at Austin, Austin, TX, 78758, USA

E-mail: deji@ece.utexas.edu

Shixuan Yang, Prof. Nanshu Lu

Department of Aerospace Engineering and Engineering Mechanics, The University of Texas at Austin, Austin, Texas, 78712, United States

#### CVD Growth and transfer process for MoS<sub>2</sub>

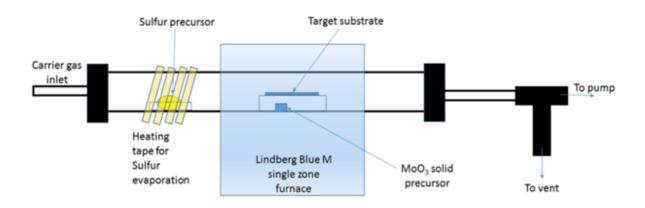

The  $MoS_2$  atomic layer films were grown by a standard vapor transfer growth process (schematic of growth setup shown in Figure S1) within a quartz tube with an inner diameter of 22 mm and a single zone Lindberg/Blue M furnace. The starting materials were  $MoO_3$  (15 mg) and sulfur (1 g) powder loaded in separate alumina crucibles, with the sulfur crucible outside the actual furnace and heated independently

<sup>[+]</sup> These authors contributed equally to this work.

using a heating tape. The substrates used for this work were surface cleaned 285 nm  $SiO_2$  on Si.

The procedure for the growth consisted of loading the starting material and the substrates, followed by pumping down to base pressure (< 10 mTorr), and followed by purging the tube and the gas lines by flowing in UHP  $N_2$  gas at 200 sccm. After 4 purging cycles the tube was filled with  $N_2$  to 1 atm pressure at flow rate of 10 sccm. Then temperature of the furnace was raised to 850 °C at a rate of 50 °C/min. When the temperature of the tube furnace was at 650 °C, the sulfur was heated to 150 °C (+/- 5 °C) and held at that temperature. The growth continued for 5 min at 850 °C, and the heater to the furnace was turned off for cooling without any feedback. Heating of the sulfur was cut off once the furnace cooled down to 650 °C.

**Figure S1**. Schematic of the  $MoS_2$  growth setup starting from  $MoO_3$  and S.

To transfer the as-grown  $MoS_2$  from  $SiO_2$  to the target substrate, PMMA (A4) was spin-coated at 4000 rpm for 40 s and baked at  $180^{\circ}$ C for 2 min. The coating and

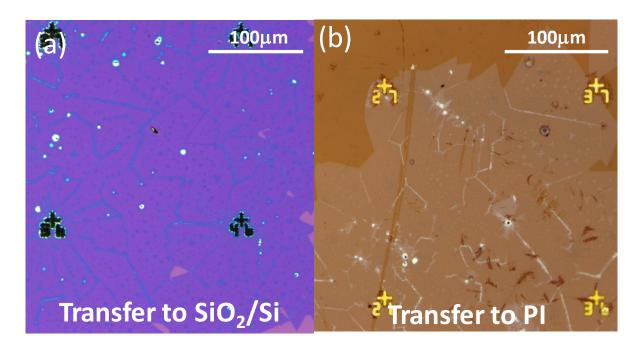

baking process was repeated four times in total. Sodium hydroxide solution (NaOH, 2M) heated at around  $80^{\circ}$ C was used to etch away the SiO<sub>2</sub> under MoS<sub>2</sub>. This enabled the PMMA-supported MoS<sub>2</sub> to be separated from the original substrate which was then transferred on to the target substrate. After the transfer, the sample was stored in the desiccator overnight and baked at  $180^{\circ}$ C for 2 min to improve the adhesion, and then soaked in acetone for 2 hours to remove the PMMA layer. Figure S2 shows the optical microscope images taken after completing the whole transfer process, showing that large area CVD MoS<sub>2</sub> can be successfully transferred to SiO<sub>2</sub> (Figure S2a) and PI (Figure S2b) substrate.

**Figure S2.** (a) and (b) are optical microscope images of CVD-growth  $MoS_2$  transferred to  $SiO_2/Si$  and polyimide substrate respectively.

#### **Material Characterization:**

Raman and PL spectroscopy were done using a Witec Alpha 300 micro-Raman confocal microscope, with the laser operating at wavelength of 488 nm. Parameters in our mapping were (i) grating (Raman) = 1800 g/mm, (PL) = 600 g/mm; (ii) integration time/pixel = 1 s; (iii) resolution =  $3 \text{ pixels/}\mu\text{m}$ .

#### Uniformity of CVD grown MoS<sub>2</sub>

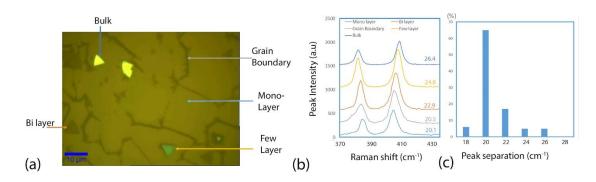

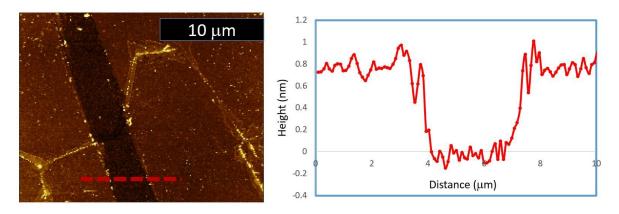

In order to show the uniformity of the CVD grown film we obtained Raman spectra from 100 points over a 2 mm x 2 mm continuous region. Raman spectrum from points 200 microns apart were taken. In Figure S3a we point out the various typical features inside the continuous monolayer region. These features include grain boundaries (two or more domains coming together), bi-layer regions, few layer regions (3-5 layers) and bulk regions (> 6 layers). Each of these regions have specific Raman spectra that correspond to different peak separations between the  $E^{1}_{2g}$  and  $A_{1g}$  peaks as shown in Figure S3b. In Figure S3c we show the frequency of these different peak separations for the 100 spectra obtained. The results show that around 70% of the film is monolayer, 18% bi-layer regions and the rest is few layer or bulk region. In addition, from AFM analysis as shown in Figure S4, a scratch was made in the center region of

large area  $MoS_2$  thin film to obtain the step height~0.8nm, which is consistent with monolayer thickness.

**Figure S3.** (a) Optical microscope image of a typical region for CVD grown  $MoS_2$ . (b) Raman spectra from regions marked in the optical image, (c) Frequency plot of peak separations for 100 points in 2 mm x 2mm area.

**Figure S4.** AFM analysis. A scratch was made in the center region of large area MoS<sub>2</sub> thin film to obtain the step height~0.8nm, which is consistent with monolayer thickness.

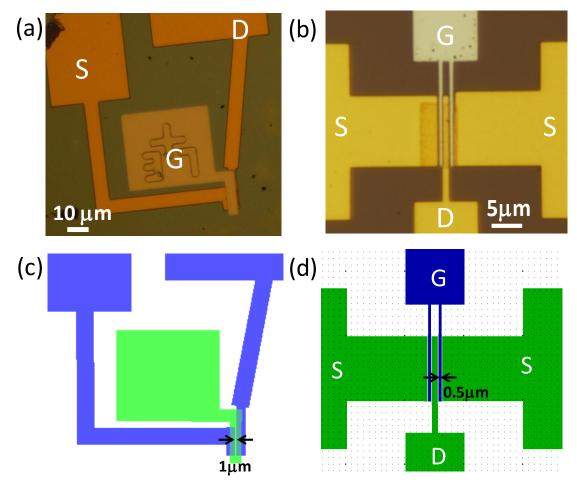

#### **Device layout on different substrates**

For device on Si, channel length is 1um determined by the gap between source and drain. For device on PI, gate length is 0.5um, and the gap between S/D and gate at each side is 0.125um. Optical image and mask design for both devices are shown in Figure S5. The contact resistance increase on flexible substrate is mainly due to the

underlap between source/drain and gate. The ungated source/drain access regions result in additional contact resistance compared to the device with overlapped source/drain and gate.

**Figure S5**. (a) Optical image for  $MoS_2$  device on Si. Channel length is  $1\mu m$  determined by the gap between source and drain. (b) Optical image for  $MoS_2$  device on PI. Gate length is  $0.5\mu m$ , and the gap between S/D and gate at each side is  $0.125\mu m$ . (c) and (d) are the mask design for device on Si and PI respectively. The physical channel dimensions are typically within  $\pm 10\%$  of the mask design.

**Table S1**. Summany for CVD-grown MoS<sub>2</sub> FET

| Gate<br>Stack &<br>Contacts  | TG/HfO <sub>2</sub><br>Ag/Au | TG/HfO <sub>2</sub><br>Ag/Au | BG/SiO <sub>2</sub><br>1T<br>MoS <sub>2</sub> | BG/SiO <sub>2</sub><br>Au | BG/SiO <sub>2</sub><br>Ti/Au | TG/HfO <sub>2</sub><br>Ti/Au |

|------------------------------|------------------------------|------------------------------|-----------------------------------------------|---------------------------|------------------------------|------------------------------|

| Max<br>Mobility<br>(cm²/V·s) | 54 <sup>a)</sup>             | 63 <sup>a)</sup>             | 56                                            | 45                        | 21 <sup>a)</sup>             | 40                           |

| $L_{g} (\mu m)$              | 1                            | 4                            | 2                                             | 10                        | 1                            | 1                            |

| Ref                          | This<br>work                 | [1]                          | [2]                                           | [3]                       | [4]                          | [5]                          |

$<sup>^{</sup>a)}$  Mobility excludes  $R_c$

#### **Device performance variation**

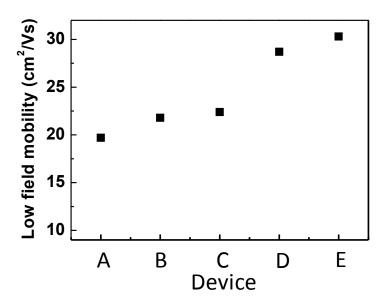

The low field mobility extracted from different devices on PI is in the range of  $19\sim31~\text{cm}^2/\text{V}\text{s}$  attributed to slight material variations and device-device variations from microfabrication (Figure S6). A representative  $G_m$  versus  $V_G$  of the device on PI is shown in Figure S7.

**Figure S6**. The low-field mobility extracted from different devices on PI is in the range of  $19\sim31~\text{cm}^2/\text{V}\text{s}$ .

Figure S7. A representative  $G_m$  versus  $V_G$  of the device on PI.

#### **Device flexibility**

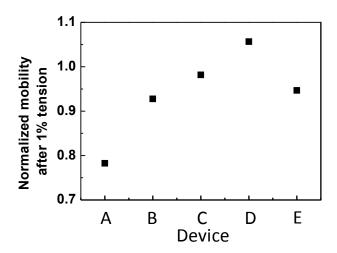

According to previous studies, cracks formation happens in high-k dielectric under  $\sim$ 2% tensile strain, and the device may fail. As a result, DC performance under 1% was selected to verify the device flexibility. As shown in Figure S8, our devices show device stability within  $\pm$ 10% change for 4 out of 5 devices. We attribute slight sliding between the metal contact to MoS<sub>2</sub> as the main reason affecting the device performance under strain, since no cracks or delamination were observed. Further studies to improve the adhesion between S/D metal to MoS<sub>2</sub> are required to improve reliability under strain.

**Figure S8**. Normalized mobility after 1% tension. Our devices show device stability within ±10% change for 4 out of 5 devices.

#### **Active Mixer Analysis:**

Figure 3c shows the schematic of MoS<sub>2</sub> FET based mixer. The gate input  $(v_G)$  of this mixer is the sum of the RF input  $(v_{RF})$  and the LO signal  $(v_{LO})$ .

$$v_G = v_{RF} + v_{LO} \tag{S1}$$

Where  $v_{RF} = A_{RF} \cos(\omega_{RF} t)$ ;  $A_{RF}$  and  $\omega_{RF}$  are the amplitude and frequency of RF input, respectively;

$v_{LO} = A_{LO} \cos(\omega_{LO} t)$ ;  $A_{LO}$  and  $\omega_{LO}$  are the amplitude and frequency of LO input, respectively.

Substituting  $v_{RF}$  and  $v_{LO}$  into Equation S1 yields

$$v_G = A_{RF} \cos(\omega_{RF} t) + A_{LO} \cos(\omega_{LO} t)$$

(S2)

MoS<sub>2</sub> FET is biased in the current saturation region, where the output drain current can be approximated by a second-order series

$$I_D = a_0 + a_1 * v_G + a_2 * v_G^2 \tag{S3}$$

Substituting Equation S2 in Equation S3

$$I_D = a_0 + a_1 (A_{RF} \cos(\omega_{RF} t) + A_{LO} \cos(\omega_{LO} t)) + a_2 (A_{RF} \cos(\omega_{RF} t) + a_2 \cos(\omega_{RF} t))$$

$$A_{LO}\cos(\omega_{LO}t))^2 + higher order terms$$

(S4)

Expanding

$$I_D = a_0 + a_1 A_{RF} \cos(\omega_{RF} t) + a_1 A_{LO} \cos(\omega_{LO} t) + a_2 \frac{A_{RF}^2}{2} (1 + \cos(2\omega_{RF} t)) + a_2 \frac{A_{LO}^2}{2} (1 + \cos(2\omega_{LO} t)) + a_3 \frac{A_{LO}^2}{2} (1 + \cos(2\omega_{LO} t)) + a_4 \frac{A_{LO}^2}{2} (1 + \cos(2\omega_{LO} t)) + a_5 \frac{A_{LO}^2}{2} (1$$

$$A_{RF}A_{LO}a_2\left(\cos((\omega_{RF}-\omega_{LO})t)+A_{RF}A_{LO}a_2(\cos(\omega_{RF}+\omega_{LO})t)+A_{RF}A_{LO}a_2(\cos(\omega_{RF}+\omega_{LO})t)\right)$$

In Equation S5 the down converted signal is shown in red. We also observe higher order frequency components at  $\omega_{RF}$ ,  $\omega_{LO}$ ,  $(\omega_{RF} + \omega_{LO})$ , .... These can be filtered by passing mixer output through low pass filter.

#### **Amplitude Modulation (AM) Receiver Analysis**

AM signal is given by

$$v_{AM} = A_C (1 + B * m(t)) \cos(\omega_C t)$$

(S6)

Where  $A_C$  is carrier amplitude,  $\omega_c$  is carrier frequency, m(t) is modulating signal, B is modulation index

The input gate voltage of FET in Figure 3e is given by

$$v_G = v_{AM} + v_C \tag{S7}$$

Where  $v_{AM}$  is the AM signal received by the antenna (Equation S6) and  $v_C$  is the local carrier signal having same frequency and phase of the carrier signal used for AM generation.

Expanding

$$v_G = A_C (1 + B * m(t)) \cos(\omega_C t) + A_C \cos(\omega_C t)$$

(S8)

Flexible MoS<sub>2</sub> FET is biased in the current saturation region, where similar to above analysis, the output drain current can be approximated by a second-order power series given by

$$I_d = a_0 + a_1 * v_G + a_2 * v_G^2 \tag{S9}$$

Substituting  $v_G$  into Equation S9 yields

$$I_{d} = a_{0} + a_{1} * \{A_{C}(1 + B * m(t)) \cos(\omega_{C}t) + A_{C} \cos(\omega_{C}t)\} + a_{2} * \{A_{C}(1 + B * m(t)) \cos(\omega_{C}t) + A_{C} \cos(\omega_{C}t)\}^{2}$$

(S10)

Expanding

$$I_d = a_0 + a_1 * \{A_C(1 + B * m(t)) \cos(\omega_C t)\} + a_1 * \{A_C \cos(\omega_C t)\} + a_2 *$$

$$\{A_C(1+B*m(t))\cos(\omega_C t)\}^2 + a_2*\{A_C\cos(\omega_C t)\}^2 + 2*a_2*A_C(1+B*m(t))$$

$$m(t)$$

)  $\cos(\omega_C t) * A_C \cos(\omega_C t)$  (S11)

Equation S11 has frequency components at DC,  $\omega_m$ ,  $(\omega_c - \omega_m)$ ,  $(\omega_c + \omega_m)$ ,

$(2\omega_c - \omega_m)$ ,  $(2\omega_c + \omega_m)$ , higher order terms. Expanding Equation S11 and low pass filtering ( cutoff frequency  $< \omega_c$  )

$$I_d = 2 * a_2 * A_c^2 * B * m(t)$$

(S12)

Output voltage of AM receiver

$$v_{out} = I_d * R_L$$

$$v_{out} = 2 * a_2 * A_c^2 * B * m(t) * R_L$$

(S13)

The output of AM receiver mainly depends on modulation index B, carrier amplifute  $A_c$ , load resistance  $R_L$  and device coefficient  $a_2$ .

Figure S9: AM transmitter and receiver measurement setup

#### References

- [1] A. Sanne, R. Ghosh, A. Rai, M. N. Yogeesh, S. H. Shin, A. Sharma, K. Jarvis, L. Mathew, R. Rao, D. Akinwande, S. Banerjee, Nano letters 2015.

- [2] R. Kappera, D. Voiry, S. E. Yalcin, W. Jen, M. Acerce, S. Torrel, B. Branch, S. Lei, W. Chen, S. Najmaei, APL Materials 2014, 2, 092516.

- [3] H. Schmidt, S. Wang, L. Chu, M. Toh, R. Kumar, W. Zhao, A. H. Castro Neto, J. Martin, S. Adam, B. Özyilmaz, Nano letters 2014, 14, 1909.

- [4] H. Liu, M. Si, S. Najmaei, A. T. Neal, Y. Du, P. M. Ajayan, J. Lou, P. D. Ye, Nano letters 2013, 13, 2640.

- [5] H. Wang, L. Yu, Y. Lee, W. Fang, A. Hsu, P. Herring, M. Chin, M. Dubey, L. Li, J. Kong, T. Palacios, "Large-scale 2D electronics based on single-layer MoS2 grown by chemical vapor deposition", presented at *Electron Devices Meeting (IEDM)*, 2012 *IEEE International*, 10-13 Dec. 2012, 2012.

- [6] H. Y. Chang, S. Yang, J. Lee, L. Tao, W. S. Hwang, D. Jena, N. Lu, D. Akinwande, ACS nano 2013, 7, 5446.

- [7] T. Jiang, R. Huang, Y. Zhu, Advanced Functional Materials 2014, 24, 396.