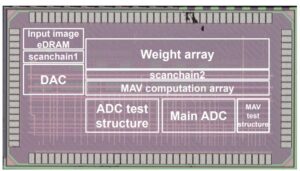

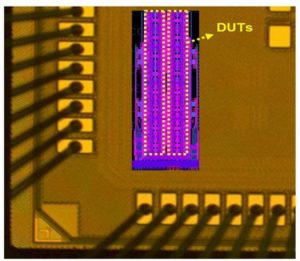

- Shanshan Xie, Can Ni, Aseem Sayal, Pulkit Jain, Fatih Hamzaoglu, and Jaydeep P. Kulkarni “eDRAM-CIM: Compute-In-Memory Design with Reconfigurable Embedded Dynamic Memory Array Realizing Adaptive Data Converters and Charge Domain Computing” IEEE International Solid State Circuits Conference (ISSCC), February 2021 [Paper] [Slides]

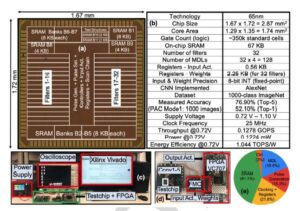

- A. Sayal, S. Fatima, S. S. Teja Nibhanupudi, and J. P. Kulkarni, “COMPAC: Compressed Time Domain, Pooling Aware Convolution CNN Engine with Reduced Data Movement for Energy-Efficient AI Computing”, IEEE Journal of Solid State Circuits (JSSC),

- All-Digital Time-Domain CNN engine using Bi-directional Memory Delay Lines for Energy Efficient Edge Computing, ISSCC 2019, Invited to JSSC Special Issue 2020

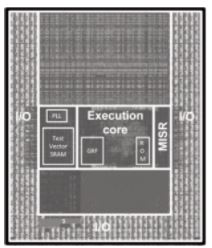

- Adaptive and resilient domino register file using in-situ timing monitors and error detection circuit , ISSCC 2015, invited to JSSC, 2016

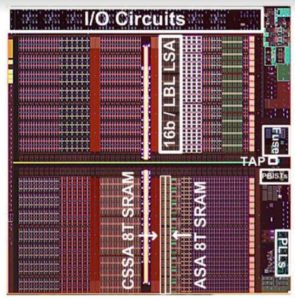

- Impacts of aging on domino-read, static differential write and retention of a 8T SRAM array, VLSI Symposium, 2017

- Post-silicon voltage guard band reduction using adaptive voltage scaling and dynamic power gating, ISSCC 2016, Special issue JSSC 2017

- Wide voltage range operation with digitally controlled fully integrated voltage regulator, ISSCC 2015, Special issue JSSC 2016

- Energy efficient graphics processor core with adaptive clocking, selective boosting, and state-retention sleep, ISSCC 2014

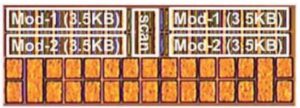

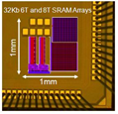

- Small signal, single ended, asymmetric sense amplifier without using reference generator for high density (256b/bitline) 8T SRAM Array, ISSCC 2016, invited to JSSC 2017

- Dual-Vcc 8T SRAM Array using dynamic level shifting wordline decoder and column based Vcc-mux for wide voltage range applications, VLSI Symposium 2013 (Conference highlight paper)

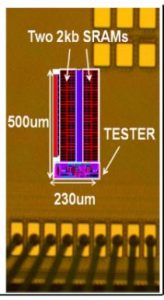

- Capacitive coupled wordline boosting for write Vmin reduction in 8T SRAM array without using any charge-pump, level shifter or separate high voltage supply, ISSCC 2012

- Schmitt Trigger based sub-threshold SRAM design (ST-2 Bitcell), TVLSI 2012, TVLSI Best Paper Award (2015)

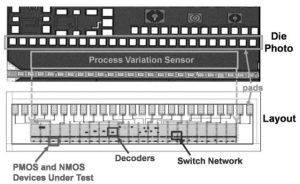

- Random Vt variation sensor using replica bias circuit, ISSCC, 2010

- Nano-spiral inductors for MRAM write current reduction, TMAG, 2010

- Random process variation characterization using high sensitivity sub-threshold sensor, TCAS-I, 2010

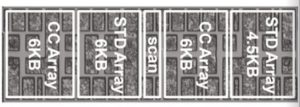

- Architecture aware, read and access time preferred SRAM design, CICC 2009

- Read-disturb free, differential sensing 8T SRAM array, TVLSI 2011

- Schmitt Trigger based robust sub-threshold SRAM design (ST-1 Bitcell), JSSC 2007